© 2023 IEEE

IEEE Access, Vol. 11, pp. 34359-34371, April 2023

# Third-Harmonic-Type Modulation Minimizing the DC-Link Energy Storage Requirement of Isolated Phase-Modular Three-Phase PFC Rectifier Systems

T. Langbauer,

D. Menzi,

V. Marugg,

F. Vollmaier,

J. Azurza,

M. Kasper,

J. W. Kolar

Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works

**Note:** This version has been updated compared to the conference version; equation (11), (12), and (13) have been corrected. This does not affect the paper's main results nor conclusions.

Date of publication xxxx 00, 0000, date of current version xxxx 00, 0000.

Digital Object Identifier 10.1109/ACCESS.2017.DOI

# Analysis of Third-Harmonic-Type Modulation Concepts Minimizing the DC-Link Energy Storage Requirement of Star- and Delta-Connected AC/DC Converter Modules of Three-Phase Isolated PFC Rectifier Systems

THOMAS LANGBAUER<sup>1</sup>, Member, IEEE, DAVID MENZI<sup>2</sup>, Member, IEEE, VALENTIN MARUGG<sup>2</sup>, FRANZ VOLLMAIER<sup>1</sup>, JON AZURZA<sup>3</sup>, Member, IEEE, MATTHIAS KASPER<sup>3</sup>, Member, IEEE, AND JOHANN W. KOLAR.<sup>2</sup>, Fellow, IEEE

<sup>1</sup>Division Power Electronics, Silicon Austria Labs GmbH (SAL), Austria (e-mail: thomas.langbauer@silicon-austria.com)

Corresponding author: Thomas Langbauer (e-mail: thomas.langbauer@silicon-austria.com).

This work has been partially supported by Silicon Austria Labs (SAL), owned by the Republic of Austria, the Styrian Business Promotion Agency (SFG), the Federal State of Carinthia, the Upper Austrian Research (UAR), and the Austrian Association for the Electric and Electronics Industry (FEEI).

ABSTRACT A three-phase ac/dc converter with high-frequency isolation can be realized as a monolithic three-phase or as a phase-modular system by combining three single-phase Power Factor Correction (PFC) rectifier modules with individual isolated dc-dc converters. Advantageously, for a phase-modular system the module configuration can be changed depending on the instantaneous input-output voltage ratio (i.e., a star-(Y)- or a delta-(Δ)-arrangement such that wide voltage ranges can be covered without a massive over-dimensioning of the main power components. However, the main disadvantage of a phase-modular converter realization is the fact that the input power of each PFC rectifier module pulsates at twice the mains frequency (which is inherent to single-phase power conversion) such that large dc-link capacitors are required. Recent literature predicts a substantial power pulsation reduction enabled by means of third-(3<sup>rd</sup>)-harmonic injection modulation which is applicable for the Y-connection (where a common-mode (CM) / zero-sequence (ZS) voltage is injected), and for the Δ-connection of the three single-phase PFC rectifier modules (where a CM / ZS current is injected). This changes the distribution of the power flow in the three-phase system and the power pulsation is shifted to higher frequencies.

This paper experimentally verifies and extends the dc-link energy storage requirement reduction of the  $3^{rd}$ -harmonic injection modulation concept: In a first step, the derivation of the harmonic injection concept is recapitulated and suitable control methods are discussed for both CM voltage (Y-arrangement) and CM current ( $\Delta$ -arrangement) injection. Further, an alternative CM voltage injection strategy with simplified reference generation based only on the instantaneous grid voltage measurements is presented and compared to the pure  $3^{rd}$ -harmonic injection modulation. Measurement results obtained from a 6 kW prototype reveal a dc-link voltage variation and/or energy buffering reduction by up to 38.6 % enabled by the harmonic injection modulation compared to conventional operation without  $3^{rd}$ -harmonic injection modulation.

**INDEX TERMS** ac-dc converter, three-phase, modular, harmonic injection, zero sequence, CM voltage injection, CM current injection

<sup>&</sup>lt;sup>2</sup>Power Electronic Systems Laboratory (PES), ETH Zurich, Switzerland (e-mail: menzi@lem.ee.ethz.ch)

<sup>&</sup>lt;sup>3</sup>Infineon Technologies Austria AG, Austria (e-mail: Jon.Azurza@infineon.com)

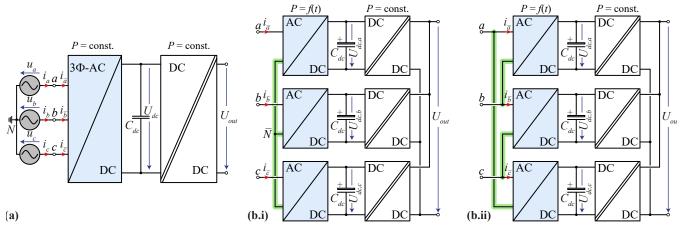

Fig. 1. Converter concepts for the realization of a three-phase ac-dc converter systems with HF isolation: (a) Monolithic three-phase Power Factor Correction (PFC) rectifier front-end combined with an isolated dc-dc converter output stage, (b) phase-modular realization comprising three single-phase ac-dc PFC rectifier front-ends combined with individual isolated dc-dc converter stages. For the phase-modular approach the PFC rectifier front-ends can be configured in (b.i) a star (Y) or (b.ii) a delta  $(\Delta)$  arrangement.

### I. INTRODUCTION

Three-phase ac-dc converter systems with High-Frequency (HF) isolation are commonly realized by combining a monolithic three-phase PFC rectifier with an isolated dc-dc converter stage [1], [2] as highlighted in **Fig. 1(a)**. There, the PFC rectifier (e.g., a two-level boost-type rectifier) generates sinusoidal grid currents  $i_{\rm a}, i_{\rm b}, i_{\rm c}$  (with amplitude  $\hat{I}_{\rm ac}$ ) in phase with the respective grid voltages  $u_{\rm a}, u_{\rm b}, u_{\rm c}$  (with line-to-neutral amplitude  $\hat{U}_{\rm ac}$ ). Advantageously, the instantaneous three-phase Low-Frequency (LF) input power sums up to a constant value which is processed by the isolated dc-dc converter stage (e.g., a Series-Resonant Converter (SRC) or a Dual-Active Bridge (DAB) [3], [4]) such that the dc-link capacitor  $C_{\rm dc}$  is only sized based on a HF and not an LF dc-link voltage criterion with typical capacitance values in the range of  $10\,\mu{\rm F/kW}$  [5]–[7].

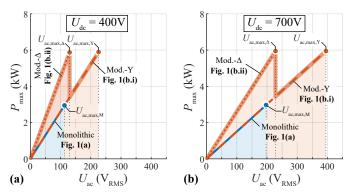

The monolithic three-phase rectifier front-end however, has two main limitations: First, for a given dc-link voltage  $U_{\rm dc}$  a boost-type rectifier with standard modulation is limited to operation with grid voltage amplitudes  $\hat{U}_{ac} \leq (1-\epsilon)\frac{U_{dc}}{2}$ where  $\epsilon$  represents a typical dc-link voltage margin to maintain grid current controllability [2]. The tolerable grid voltage range is highlighted in Fig. 2 for two dc-link voltage levels and is (for  $\epsilon=25\,\%$ ) limited to  $U_{\rm ac,max,M}\approx115\,{\rm V_{RMS}}$  for  $U_{\rm dc} = 400\,{\rm V}$  in Fig. 2(a) and  $U_{\rm ac,max,M} \approx 200\,{\rm V_{RMS}}$  for  $U_{\rm dc} = 700 \, \text{V}$  in **Fig. 2(b)**. Second, in case a wide grid input voltage range is required, e.g., to allow for compatibility with different nominal mains voltages or to tolerate fluctuating mains voltages in weak grids, the rectifier front-end is subject to high current stresses and/or can only provide a limited output power. Typically, the tolerable RMS value  $I_{\bar{i}}$  of the rectifier input currents  $i_{\bar{a}}, i_{\bar{b}}, i_{\bar{c}}$  (here  $I_{\bar{i}} = I_{ac}$ ) is limited by the dimensioning of the magnetic components or the power semiconductors and hence, the maximum transmittable power  $P_{\rm max}$  presented in Fig. 2 is proportional to the

Fig. 2. Maximum transmittable power  $P_{\rm max}$  of a boost-type three-phase rectifier front-end as a function of the three-phase line-to-neutral grid voltage  $U_{\rm ac}$  for (a) a dc-link voltage of  $U_{\rm dc}=400\,{\rm V}$  and a maximum rectifier input current of  $I_{\bar{\rm j}}=8.7\,{\rm A_{RMS}}$  (i.e., a nominal system power of  $6\,{\rm kW}$  for an input voltage of  $U_{\rm ac}=230\,{\rm V_{RMS}}$ ), and (b) a dc-link voltage of  $U_{\rm dc}=700\,{\rm V}$  and a maximum rectifier input current of  $I_{\bar{\rm j}}=5.0\,{\rm A_{RMS}}$  (i.e., a nominal system power of  $6\,{\rm kW}$  for an input voltage of  $U_{\rm ac}=400\,{\rm V_{RMS}}$ ). The considered rectifier front-end concepts are: the monolithic three-phase PFC rectifier from Fig. 1(a), and the phase-modular PFC rectifier in star (Y) or delta ( $\Delta$ ) arrangement from Fig. 1(b). The respective maximum tolerable input voltage (and power) operating point considering a grid current controllability voltage margin of  $\epsilon=25\,\%$  of each concept is highlighted by a round scatter point.

RMS grid voltage  $U_{\rm ac}$  and is limited for the considered example to values below  $P_{\rm max} \approx 3\,{\rm kW}.$

Converter reconfiguration is a well known concept to allow a wide ac input (and/or dc output) voltage range [8]–[10], but cannot be applied to the monolithic three-phase PFC rectifier front-end in **Fig. 1(a)**. However, the functionality of the converter in **Fig. 1(a)** can be achieved alternatively by combining three single-phase ac-dc PFC rectifier front-ends with individual isolated dc-dc converter stages [11]–[15] as highlighted in **Fig. 1(b)**. Here, the power modules

can be advantageously configured in a star (Y)-arrangement (**Fig. 1(b.i)**) or a delta ( $\Delta$ )-arrangement (**Fig. 1(b.ii**)), which allows to change the PFC rectifier front-end input voltage and current range [16]:

In Y-configuration (**Fig. 1(b.i)**) a boost-type rectifier with standard modulation is limited to  $\hat{U}_{\rm ac} \leq (1-\epsilon)U_{\rm dc}$ , i.e., an improvement by about a factor of two compared to the monolithic three-phase rectifier which is enabled by the bipolar-voltage capability and the full utilization of the dc voltage of the full-bridges in the single-phase PFC rectifier modules for generation of an ac voltage [17]. For  $\varepsilon=25\,\%$  the grid ac voltage amplitude is limited to  $U_{\rm ac,max,Y}\approx230\,{\rm V_{RMS}}$  for  $U_{\rm dc}=400\,{\rm V}$  in **Fig. 2(a)** and  $U_{\rm ac,max,Y}\approx400\,{\rm V_{RMS}}$  for  $U_{\rm dc}=700\,{\rm V}$  in **Fig. 2(b)**, corresponding to  $P_{\rm max}\approx6\,{\rm kW}$ .

Note that in Y-configuration the rectifier input current stresses are (as for the monolithic rectifier in Fig. 1(a)) directly defined by the grid current and  $I_{\bar{\rm j}}=I_{\rm ac}$ . If the configuration is now changed to a  $\Delta$ -arrangement of the modules as highlighted in Fig. 1(b.ii), each module is subject to the grid line-to-line voltage with an amplitude of  $\sqrt{3}\hat{U}_{\rm ac}$  and hence the module current stresses are reduced to  $I_{\bar{\rm j}}=I_{\rm ac}/\sqrt{3}$  such that  $P_{\rm max}\approx 6\,{\rm kW}$  can be achieved for lower grid voltage levels in Fig. 2. Here, the maximally tolerable grid voltage amplitude is limited to  $\sqrt{3}\hat{U}_{\rm ac}\leq (1-\epsilon)U_{\rm dc}$ , such that  $U_{\rm ac,max,\Delta}\approx 130\,{\rm V_{RMS}}$  for  $U_{\rm dc}=400\,{\rm V}$  in Fig. 2(a) and  $U_{\rm ac,max,\Delta}\approx 230\,{\rm V_{RMS}}$  for  $U_{\rm dc}=700\,{\rm V}$  in Fig. 2(b), corresponding to  $P_{\rm max}\approx 6\,{\rm kW}$ .

Hence, the module configuration can be changed depending on the grid voltage level of the considered application which allows to cut the voltage or current stresses by a factor of  $\sqrt{3}$  (see **Tab. 1**). Further, such a phase-modular realization features a high failure tolerance [13] and the system can continue operation with reduced output power in case one or even two converter modules fail. The main weakness of a phase-modular converter realization is, however, the fact that the input power of each PFC rectifier module pulsates at twice the mains frequency (which is inherent to single-phase power conversion) such that large dc-link capacitors  $C_{\rm dc}$  are required, which may cover a large fraction of the overall converter volume and/or limit the system lifetime [18], [19].

Hence, several measures to reduce the dc-link power pulsation and/or the minimally required dc-link capacitance value of phase-modular three-phase PFC rectifier systems are investigated in literature: Active power pulsation buffers [20]–[22] allow a higher capacitor utilization, but require additional power components and result in elevated overall conversion losses compared to passive buffering with electrolytic capacitors [21]. Alternatively, as in sum the instantaneous grid input power is constant, the pulsating input power can be redistributed by the subsequent isolated dc-dc converter stages (see Fig. 3(a)) as investigated in [14], [15], [23]. This approach, however, comes at the cost of elevated component stresses and conversion losses of the dc-dc converters and ideally the power pulsation is already reduced in the acdc front-ends. In [24] the power pulsation of a low power single-phase ac-dc converter is reduced by regulating a non-

**TABLE 1:** SYSTEM SPECIFICATIONS<sup>1</sup>.

| Design.                                 | Description                                                                | Value                                                                                                                                 |

|-----------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| $U_{ m ac}$ $I_{ m ac}$ $f_{ m ac}$ $P$ | Grid voltage (line-to-neutral) Grid current Grid frequency Input power     | $\begin{array}{c} 3{\times}230\mathrm{V_{RMS}} \\ 3{\times}8.7\mathrm{A_{RMS}} \\ 50\mathrm{Hz} \\ 3{\times}2\mathrm{kW} \end{array}$ |

| $I_{ar{	ext{j}}} \ U_{	ext{dc,j}}$      | LF input current (Y-config.) dc-link voltage (Y-config.)                   | $3\times8.7\mathrm{A_{RMS}}$ $400\mathrm{V}$                                                                                          |

| $I_{ar{	ext{j}}} \ U_{	ext{dc,j}}$      | LF input current ( $\Delta$ -config.) dc-link voltage ( $\Delta$ -config.) | $3\times5.0\mathrm{A_{RMS}}$ $700\mathrm{V}$                                                                                          |

|                                         |                                                                            |                                                                                                                                       |

$j \in \{a, b, c\}$

sinusoidal grid current, which comes at the cost of a high grid current distortion and therefore cannot be scaled to higher power levels. In contrast to a standalone single-phase ac-dc converter, the phase-modular realization of a three-phase ac-dc converter features an additional degree of freedom for the modulation given by the Common-Mode (CM) voltage  $u_{\rm CM}$  (in Y-configuration, see Fig. 3(a)) or the CM current  $i_{\rm CM}$  (in  $\Delta$ -configuration, see Fig. 3(e)), that do not impact the grid currents (in contrast to [24] the grid currents remain fully sinusoidal) but allow to influence the distribution of the (instantaneously constant) overall three-phase input power flow to the three front-end single-phase PFC rectifier modules [1] and/or to shift the module input power pulsations to higher frequencies.

The concept of a power pulsation reduction by means of harmonic injection was investigated in [1] based on simulations only, and the main goal of this paper is to provide a hardware verification of the proposed modulation concept and the reduction of the dc-link energy buffering requirement based on a  $6\,\mathrm{kW}$  hardware demonstrator (the main specifications are listed in **Tab. 1**) allowing both Y- and  $\Delta$ -configuration of the modules.

The publication comprises two main Sections. First, Section II covers the Y-connected operation of the converter modules: The theoretical background of harmonic voltage injection and its impact on the module power flow is recapitulated. Further, harmonic injection by means of Space Vector Modulation (SVM) is considered. Then, a suitable control structure for PFC rectifier operation with harmonic voltage injection is presented. Last, details on the hardware prototype and experimental waveforms confirming the predicted energy buffering reduction are presented. Then, Section III covers all relevant aspects of the  $\Delta$ -connected operation of the converter modules again including the experimental verification. Last, Section IV summarizes the main findings of the paper and presents an outlook to further research on harmonic injection techniques for phase-modular three-phase isolated PFC rectifier systems.

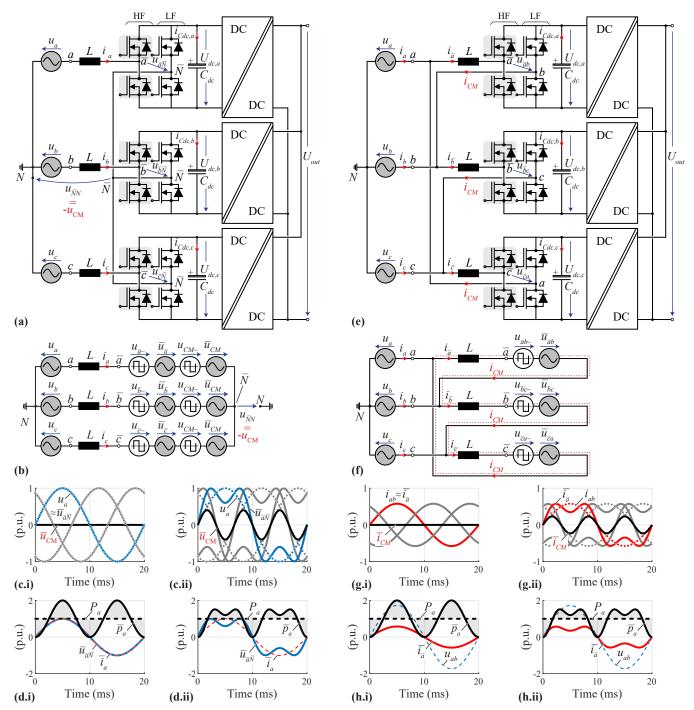

Fig. 3. (a) Phase-modular realization of the ac-dc converter employing a Y-connection of single-phase PFC rectifier modules with individual isolated dc-dc converter stages and dc-link voltages around  $400\,\mathrm{V}$  for a typical peak grid line-to-neutral voltage of  $325\,\mathrm{V}$ . (b) ac-side equivalent circuit of the converter shown in (a) with separate and high-frequency DM and CM module input voltage sources of the PFC rectifier switching stages. (c) Waveforms of the grid phase voltages and of the LF components of the input voltages of the rectifier switching stages and of the injected CM voltage for (c.i)  $M_3 = 0$  and (c.ii)  $M_3 = 0.4$ . (d) Phase a switching stage LF input voltage  $\bar{u}_{\bar{a}\bar{N}}$ , current  $\bar{i}_a$  and power  $\bar{p}_a$  within one mains period for a  $3^{\mathrm{rd}}$  harmonic voltage modulation index of (d.i)  $M_3 = 0$  and (d.ii)  $M_3 = 0.4$ . Note, that the average input power  $P_a$  is represented by a dashed line and is not impacted by  $M_3$ .

(e) Phase-modular realization of the ac-dc converter employing a  $\Delta$ -connection of single-phase PFC rectifier modules with individual isolated dc-dc stages and dc-link voltages around 700 V. (f) ac-side equivalent circuit of the converter shown in (e) with separate LF and high-frequency equivalent input voltage sources of the PFC rectifier stages. (g) Waveforms of the grid phase currents and of the LF components of the input currents of the rectifier switching modules and of the CM current  $i_{\rm CM}$  circulating inside the  $\Delta$ -connection for (g.i)  $M_3=0$  and (g.ii)  $M_3=0.4$ . (h) Phase a switching stage LF input voltage  $\bar{u}_{\bar{n}\bar{N}}$ , current  $\bar{t}_a$  and power  $\bar{p}_a$  within one mains period for a  $3^{\rm rd}$  harmonic current modulation index of (h.i)  $M_3=0$  and (h.ii)  $M_3=0.4$ . (Figure adapted from [1])

# II. STAR-(Y)-CONNECTED PHASE-MODULAR CONVERTER

### A. THEORY

The three single-phase isolated PFC rectifier modules in Y-configuration are shown in **Fig. 3(a)**, where the rectifier modules are realized with a totem pole structure [17], [25], [26], i.e., a fast-switching HF half-bridge is combined with an LF unfolder bridge-leg such that high conversion efficiency results. The grid voltages and currents of phase  $j \in \{a, b, c\}$  are defined by

$$u_{j} = \hat{U}_{ac} \sin(\omega_{ac}t + \phi_{j})$$

$$i_{j} = \hat{I}_{ac} \sin(\omega_{ac}t + \phi_{j}),$$

(1)

with the grid (line-to-neutral) voltage  $\hat{U}_{\rm ac}$  and current  $\hat{I}_{\rm ac}$  amplitude and the grid angular frequency  $\omega_{\rm ac}=2\pi f_{\rm ac}$  and phase angles  $\phi_{\rm a}=0,\phi_{\rm b}=-\frac{2\pi}{3}$  and  $\phi_{\rm c}=-\frac{4\pi}{3}$  (see **Tab. 1**). In **Fig. 3(a)** the module starpoint  $\bar{N}$  is not connected to

In **Fig. 3(a)** the module starpoint N is not connected to the grid starpoint N and therefore, the grid input currents  $i_{\rm a}, i_{\rm b}, i_{\rm c}$  sum up to zero and are not impacted by a CM voltage  $u_{\rm \bar{N}N}$  in between  $\bar{N}$  and N. CM voltage injection [27] was originally introduced to extend the linear operating range of motor drive inverters. However, the CM voltage offset can also employed to reduce the current stresses in Y-configured splitbattery applications [28] or phase-modular isolated rectifier systems [1].

The ac-side equivalent circuit from [1] for the Y-configuration of the converter modules is shown in **Fig. 3(b)**. There the rectifier front-end switch-node voltages are decomposed into Differential-Mode (DM) / CM and LF / HF components, e.g., for phase module a the switch-node voltage  $u_{\bar{a}\bar{N}}$  is represented by

- the HF DM voltage  $u_{\bar{\mathbf{a}}\sim}$ ,

- the LF DM voltage  $\bar{u}_{\bar{\mathrm{a}}} \approx u_{\mathrm{a}},$

- the HF CM voltage  $u_{\rm CM}$ , and,

- the LF CM voltage  $\bar{u}_{\rm CM}$ ,

with  $u_{\bar{\rm NN}}=-(\bar{u}_{\rm CM}+u_{\rm CM\sim})$  and  $\bar{u}_{\rm CM}$  is set by the harmonic injection modulation.

The considered single-phase converter module structure in **Fig. 3(a)** is a boost-type system [2], i.e., the condition for grid current controllability is given by

$$\bar{u}_{\bar{i}\bar{N}}(t) \le U_{dc,j}(t),$$

(2)

thereby imposing a limit to the maximum module LF dc-link voltage fluctuation and/or a minimum dc-link capacitance value  $C_{\rm dc}$  [29]. Further,  $C_{\rm dc}$  needs to be sized such that the maximum dc-link voltage  $U_{\rm dc.max}$  is not exceeded, i.e.,

$$U_{\text{dc.i}}(t) \le U_{\text{dc.max}},$$

(3)

with  $U_{\rm dc,max}$  typically defined by the maximally tolerable semiconductor blocking voltage. For  $600\,\rm V$  power semiconductors, typically  $U_{\rm dc,max}=420\,\rm V$  is employed corresponding to a  $30\,\%$  blocking voltage margin to account for transient switch-node overvoltages.

The dc-link voltage  $U_{\mathrm{dc,j}}$  variation is a function of the LF module input power  $\bar{p}_{\mathrm{j}}$  which is defined by  $\bar{u}_{\mathrm{\bar{j}}\mathrm{\bar{N}}}$  and the

corresponding LF module input current  $ar{i}_{ar{\mathbf{j}}}$  as

$$\bar{p}_{\mathbf{j}}(t) = \bar{u}_{\mathbf{\bar{j}}\bar{\mathbf{N}}}(t) \cdot \bar{i}_{\mathbf{\bar{j}}}(t) = (\bar{u}_{\bar{\mathbf{a}}}(t) + \bar{u}_{\mathrm{CM}}(t)) \cdot \bar{i}_{\mathbf{\bar{j}}}(t). \tag{4}$$

Hence, the module input power flow can be adjusted by means of setting a suitable LF CM voltage component  $\bar{u}_{\rm CM}$ . Note that with  $i_{\rm a}+i_{\rm b}+i_{\rm c}=0$  the CM voltage  $\bar{u}_{\rm CM}$  does not impact the overall power flow from the grid but redistributes power among the front-end single-phase rectifier modules.

In the following the main power flow quantities are derived, first, for conventional sinusoidal modulation (i.e., with  $\bar{u}_{\rm CM}=0$ ) and, subsequently, for two CM voltage injection strategies, i.e., 3<sup>rd</sup>-harmonic and triangular CM voltage injection, and the improvement in energy buffering and dclink voltage fluctuation are assessed. For simplicity, in the following all derivations are performed for the converter module a.

### 1) Conventional Modulation

The main ac-side terminal voltage waveforms for conventional modulation (i.e., with  $\bar{u}_{\rm CM}=0$ ) are presented in **Fig. 3(c.i),(d.i)** where the LF module input power  $\bar{p}_{\rm a}$  according to (4) results to

$$\bar{p}_{\mathrm{a}}(t) = \frac{1}{2}\hat{U}_{\mathrm{ac}}\hat{I}_{\mathrm{ac}}\left(1 - \cos(2\omega_{\mathrm{ac}}t)\right),\tag{5}$$

and comprises the well known twice-mains-frequency single-phase grid power pulsation on top of the (assuming ideally lossless power conversion) constant module output power  $P_{\rm a}=\frac{1}{2}\hat{U}_{\rm ac}\hat{I}_{\rm ac}.$  The difference of the fluctuating LF module input power  $\bar{p}_{\rm a}(t)$  and the output power  $P_{\rm a}$  is covered by the dc-link capacitor  $C_{\rm dc}$  with an energy balance

$$E_{dc,a}(t) = \frac{1}{2} C_{dc} U_{dc,a}^{2}(t)$$

$$= \int_{0}^{t} (\bar{p}_{a}(\tau) - P_{a}(\tau)) d\tau$$

$$= -\frac{\hat{U}_{ac} \hat{I}_{ac}}{4\omega_{ac}} \sin(2\omega_{ac}t) + E_{dc,a}(0),$$

(6)

with  $E_{\rm dc,a}(0)=\frac{1}{2}C_{\rm dc}U_{\rm dc}^2$ , and hence depends on the average dc-link voltage  $U_{\rm dc}=400\,\rm V$ . The dc-link LF energy buffering requirement  $\Delta E_{\rm dc,a}$  (represented by the light-gray areas in **Fig. 3(d.i)**) is defined by the difference of the maximum and minimum value of  $E_{\rm dc,a}(t)$  within a mains period  $T_{\rm ac}$  and results to

$$\Delta E_{\rm dc,a} = \max(E_{\rm dc,a}(t)) - \min(E_{\rm dc,a}(t))$$

$$= \frac{\hat{U}_{\rm ac}\hat{I}_{\rm ac}}{2\omega_{\rm ac}}.$$

(7)

With (6) the time-varying dc-link voltage  $U_{\rm dc,a}(t)$  is de-

fined by the module input power  $\bar{p}_a$  (cf., (5),(6))

$$U_{\rm dc,a}(t) = \sqrt{\frac{2}{C_{\rm dc}} E_{\rm dc,a}(t)}$$

$$= \sqrt{\frac{2}{C_{\rm dc}} \left(\frac{-\hat{U}_{\rm ac}\hat{I}_{\rm ac}}{4\omega_{\rm ac}} \sin(2\omega_{\rm ac}t) + E_{\rm dc,a}(0)\right)},$$

(8)

and hence the peak-to-peak dc-link LF voltage fluctuation  $\Delta U_{\rm dc,a}$  results to

$$\Delta U_{\rm dc,a} = \sqrt{\frac{2}{C_{\rm dc}}} \left( \sqrt{\max(E_{\rm dc,a}(t))} - \sqrt{\min(E_{\rm dc,a}(t))} \right)$$

$$= \frac{\Delta E_{\rm dc,a}}{C_{\rm dc}U_{\rm dc}} = \frac{\hat{U}_{\rm ac}\hat{I}_{\rm ac}}{2\omega_{\rm ac}C_{\rm dc}U_{\rm dc}}, \tag{9}$$

i.e., is proportional to the dc-link LF energy buffering requirement. The calculated values of  $\Delta E_{\rm dc,a}$  and  $\Delta U_{\rm dc,a}$  according to the considered converter specifications in **Tab. 1** and **Tab. 2** are provided in **Tab. 3**.

In the following, the voltage  $\bar{u}_{\rm CM}$  is used to adjust the LF module input power  $\bar{p}_{\rm a}$  such that the energy buffering requirement  $\Delta E_{\rm dc,a}$  and the fluctuation of the dc-link voltage  $\Delta U_{\rm dc,a}$  is reduced.

### 2) 3rd-Harmonic CM Voltage Injection

For 3<sup>rd</sup>-harmonic injection modulation, the LF CM voltage component is defined by

$$\bar{u}_{\rm CM}(t) = M_3 \hat{U}_{\rm ac} \sin(3\omega_{\rm ac}t + \varphi_3), \tag{10}$$

where  $M_3 = \hat{U}_{\rm CM}/\hat{U}_{\rm ac}$  represents the 3<sup>rd</sup>-harmonic modulation index and  $\varphi_3$  the corresponding phase angle. In **Fig. 3(c.ii,d.ii)** the characteristic waveforms of module a are illustrated for a 3<sup>rd</sup>-harmonic voltage injection with  $M_3 = 0.4$ . The LF module input power  $\bar{p}_a$  according to (4) results to (for  $\varphi_3$ =0),

$$\bar{p}_{a}(t) = \frac{1}{2}\hat{U}_{ac}\hat{I}_{ac}\left(1 - (1 - M_3)\cos(2\omega_{ac}t) - M_3\cos(4\omega_{ac}t)\right), \tag{11}$$

i.e., with increasing values of  $M_3$  the twice-mains frequency power pulsation is shifted from  $2f_{\rm ac}$  to  $4f_{\rm ac}$ . The  $3^{\rm rd}$ -harmonic phase shift value  $\varphi_3$  further allows to optimize the LF module input voltage  $\bar{u}_{\bar{a}\bar{N}}$  with respect to the current controllability dc-link voltage margin (for more details please see [1]) and the module input power  $\bar{p}_{\rm a}(t)$  results to

$$\bar{p}_{a}(t) = \frac{1}{2}\hat{U}_{ac}\hat{I}_{ac}\left(1 - \cos(2\omega_{ac}t) + M_3\cos(2\omega_{ac}t + \varphi_3)\right) - M_3\cos(4\omega_{ac}t + \varphi_3)\right). \tag{12}$$

Combining (6) and (12) the energy stored in  $C_{\rm dc}$  under

3<sup>rd</sup>-harmonic modulation results to

$$E_{\rm dc,a}(t) = \frac{1}{8\omega_{\rm ac}} \hat{U}_{\rm ac} \hat{I}_{\rm ac} \left(-2\sin(2\omega_{\rm ac}t) + 2M_3\sin(2\omega_{\rm ac}t + \varphi_3) - M_3\sin(4\omega_{\rm ac}t + \varphi_3)\right) + E_{\rm dc,a}(0).$$

(13)

Here, the analytic expression for the energy buffering requirement  $\Delta E_{\rm dc,a}$  is rather involved and therefore omitted. However,  $\Delta E_{\rm dc,a}$  can be easily calculated numerically from (13) and is provided in **Tab. 3**. Compared to conventional operation, i.e., with  $M_3=0$  and  $\Delta E_{\rm dc,a}=6.4\,\rm J$  (depicted in **Fig. 3(d.ii)**), the buffered energy  $E_{\rm dc,a}$  for  $M_3=0.4$  in **Fig. 3(d.ii)** is reduced by 30 % and  $E_{\rm dc,a}$  can be further reduced by up to a factor of two for  $M_3=1.0$  (which however would require a higher dc-link voltage level to maintain current controllability according to (2)).

Combining (6) and (11) the time-varying dc-link voltage  $U_{\rm dc,a}(t)$  results to

$$U_{\rm dc,a}(t) = \left(\frac{2}{C_{\rm dc}} \left(\frac{1}{8\omega_{\rm ac}} \hat{U}_{\rm ac} \hat{I}_{\rm ac} \left(-2\sin(2\omega_{\rm ac}t) + 2M_3\sin(2\omega_{\rm ac}t + \varphi_3) - M_3\sin(4\omega_{\rm ac}t + \varphi_3)\right) + E_{\rm dc,a}(0)\right)\right)^{0.5}.$$

(14)

The peak-to-peak dc-link LF voltage fluctuation  $\Delta U_{\rm dc,a}$  results again in an excessively long analytic expression, and is hence calculated numerically from (14).

### 3) Triangular CM Voltage Injection

Aiming at a symmetric three-phase system, any CM voltage comprising voltage components at multiples of the triplemains frequency  $3f_{\rm ac}$  can be considered. Here, a triangular CM voltage is considered which is implicitly generated by Space Vector Modulation (SVM). The SVM concept originates from the field of motor drive inverter systems and here, the main benefit of SVM is the fact that — in contrast to the  $3^{\rm rd}$ -harmonic injection modulation — no Phase-Locked Loop (PLL) is required to generate a CM voltage reference at multiples of  $3f_{\rm ac}$ : The triangular SVM LF CM voltage reference is generated solely based on the measured instantaneous module input voltages  $u_{\bar{a}\bar{N}}$ ,  $u_{\bar{b}\bar{N}}$ ,  $u_{\bar{c}\bar{N}}$  and is defined as

$$\bar{u}_{\mathrm{CM}}(t) = -M_{\mathrm{SVM}}(\max(u_{\bar{\mathbf{a}}\bar{\mathbf{N}}}, u_{\bar{\mathbf{b}}\bar{\mathbf{N}}}, u_{\bar{\mathbf{c}}\bar{\mathbf{N}}}) + \min(u_{\bar{\mathbf{a}}\bar{\mathbf{N}}}, u_{\bar{\mathbf{b}}\bar{\mathbf{N}}}, u_{\bar{\mathbf{c}}\bar{\mathbf{N}}})), \tag{15}$$

with  $M_{\rm SVM}$  the harmonic injection modulation index and  $\max(\bar{u}_{\rm CM}) = \frac{1}{2} M_{\rm SVM} \hat{U}_{\rm ac}$ . Note that the negative sign in (15) facilitates a decrease of the maximum instantaneous phase voltage and  $M_{\rm SVM} = 0.5$  is traditionally employed in drive applications in order to maximize the dc-link voltage utilization similar to  $3^{\rm rd}$ -harmonic injection modulation with  $M_3 = 1/6$ .

Due to the additional frequency components in  $\bar{u}_{\rm CM}(t)$  the analytic expressions for  $E_{\rm dc,a}(t)$ ,  $\Delta E_{\rm dc,a}$ ,  $U_{\rm dc,a}(t)$ , and  $\Delta U_{\rm dc,a}$  are rather involved. However 3<sup>rd</sup>-harmonic and trian-

gular CM voltage injection can be compared qualitatively by considering the Fourier coefficient of the frequency decomposition of (15) which can be approximated by

$$b_{\rm n} = \frac{1}{2} M_{\rm SVM} \hat{U}_{\rm ac} \frac{8}{\pi^2} \frac{(-1)^{(\frac{n}{3}-1)/2}}{(\frac{n}{3})^2}, \tag{16}$$

with n=3,9,15,... at multiples of  $3f_{\rm ac}$ . Hence, for  $M_{\rm SVM}=1.0$  the Fourier coefficient at n=3 results to  $b_3\approx 0.4\cdot \hat{U}_{\rm ac}$ , and hence (when neglecting the impact of the additional frequency components at n>3) the energy buffering reduction is similar to  $3^{\rm rd}$ -harmonic voltage injection with  $M_3=0.4$ , which is confirmed by the calculated vales of  $\Delta E_{\rm dc,a}$  and  $\Delta U_{\rm dc,a}$  in **Tab. 3**.

### B. CONTROL CONCEPT

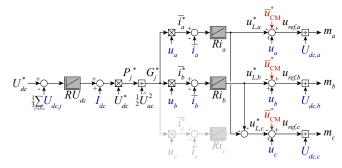

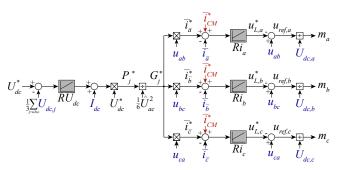

Fig. 4 illustrates the cascaded control concept for the phase modular three ac-dc converter in Y-configuration (see Fig. 3(a)) with an outer low-bandwidth dc-link voltage controller  $RU_{\rm dc}$  (regulating the average dc-link voltage value of the three modules) and two fast grid current controllers  $Ri_j$   $(j \in \{a,b\})$ :

First,  $RU_{\rm dc}$  defines an equal power reference  $P_{\rm j}$  for all modules. Note that instability might occur in case of individual dc-link voltage controllers due to the three-phase coupling of the rectifier modules as highlighted in [1], [12], [30]. Note that this control structure does not penalize a DM imbalance between the three dc-link voltages and it is assumed that the subsequent dc-dc stages assure dc-link voltage balancing in the modules. Alternatively, the dc-link balancing concept of [31], [32] could be employed.

The power reference is then translated into sinusoidal current references  $i_i^*$  in phase with each respective grid voltages by using a grid conductivity reference  $G_i^*$ . Here, only the two grid currents  $i_a$  and  $i_b$  are actively controlled by means of a current controller  $Ri_i$ , whereas  $i_c$  is inherently defined due to the open module starpoint  $\bar{N}$  implying  $i_c = -(i_a + i_b)$ . Hence, the inductor voltage reference of phase c is derived from the current controller signals of the phase module a and b with  $u_{L,c}^* = -(u_{L,a}^* + u_{L,b}^*)$ . The inductor voltage references  $u_{L,j}^*$  is subtracted from the grid phase voltage feedforward term,  $u_i$  and, finally, the LF CM voltage reference  $\bar{u}_{\rm CM}$  is added to obtain the LF switch-node voltage  $u_{{\rm ref,j}}$ . Finally, by dividing  $u_{\text{ref,j}}$  by the respective dc-link voltage  $U_{\text{dc,j}}$  the module duty-cycle  $m_j \in \{-1,1\}$  is obtained, which is translated into a Pulse Width Modulation (PWM) signal for the HF bridge-leg and a binary switching state of the unfolder bridge-leg.

As a PLL is anyway required to generate a  $3^{\rm rd}$ -harmonic CM voltage reference, the grid phase voltages  $u_j$  are calculated from the instantaneous PLL grid angle  $\omega_{\rm ac}t$  and the (low-pass filtered) measured grid voltage amplitude  $\hat{U}_{\rm ac}$  to avoid any undesired ringing or measurement noise originating from the grid voltage feedforward terms. The employed PLL is based on a Second-Order Generalized Integrator (SOGI) three-phase algorithm [33].

**Fig. 4.** Block diagram of a cascaded control of the PFC rectifier input stages of **Fig. 3(a)** considering a  $3^{rd}$  harmonic CM voltage injection  $\bar{u}_{\rm CM}^*$ . (Figure adapted from [1])

### C. EXPERIMENTAL RESULTS

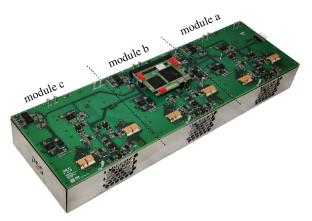

For this publication the 6 kW hardware demonstrator presented in Fig. 5 was developed according to the specifications in **Tab. 1**. The system comprises three 2 kW single-phase PFC rectifier modules which can be freely reconfigured, thereby enabling the experimental investigation of the considered modulation strategies in Y-configuration and  $\Delta$ -configuration (subject of **Section III**). Note that the prototype emulates the secondary isolated dc-dc converter stages (drawing a constant power  $P_i$  from the dc-link, see **Fig. 3a**) by three load resistors  $R_{\rm load}$  during the experiments. For the considered operating points, the dc-link voltage fluctuation(and hence for a resistive load the dc current fluctuation) remains below  $\pm 10 \%$ , such that  $R_{load}$  sufficiently approximates a constant-power load. Aiming at a flexible hardware demonstrator platform, the power module unfolder and HF bridge-leg semiconductors are realized with Silicon Carbide (SiC) Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) rated to 1.2 kV [34] and further details on the main power components are listed in Tab. 2. It is worth highlighting that in an industrial system of course semiconductors with lower rated voltage, i.e., with 600 V for Y-configuration (and with  $900 \,\mathrm{V}$  for  $\Delta$ -configuration) would be employed to maximize efficiency and minimize cost, whereas here the verification of the dc-link energy storage requirement reduction by a harmonic injection modulation is the main objective.

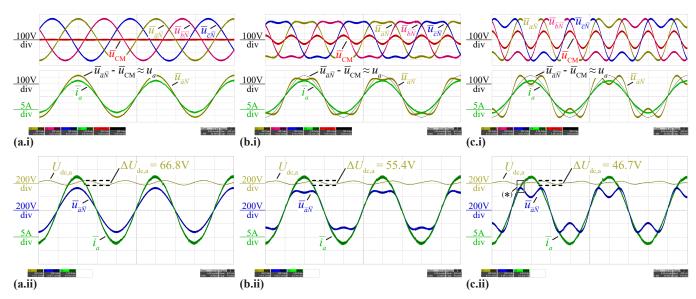

Measurement results for nominal power operation in Y-configuration are presented in Fig. 6. In case of conventional modulation (see Section II-A1) the CM voltage is set to  $\bar{u}_{\rm CM} \approx 0$  and the module input voltages  $\bar{u}_{\bar{\rm j}\bar{\rm N}}$  in Fig. 6(a.i) are purely sinusoidal and the module input current  $\bar{i}_{\rm a}$  is in phase with the respective grid voltage. Fig. 6(a.ii) further depicts the dc-link voltage of module  $a~U_{\rm dc,a}$  and the peak-to-peak dc-link voltage fluctuation results to  $\Delta U_{\rm dc,a} = 66.5~{\rm V}$  corresponding to a buffered energy  $\Delta E_{\rm dc,a} = 6.5~{\rm J}$  (obtained by integrating the measured voltage  $\bar{u}_{\bar{\rm j}\bar{\rm N}}$  and current  $\bar{i}_{\rm a}$ ) which closely match the calculated values according to (9) and (7) provided in Tab. 3.

Next, operation with a  $3^{\text{rd}}$ -harmonic voltage injection index  $M_3 = 0.2$  and  $M_3 = 0.4$  is depicted in **Fig. 6(b)** and (c), respectively. There, the module input current  $\bar{i}_a$  is

| TARLE 2. MAIN POWER | COMPONENTS OF THE HARDWARE DEMONSTRATOR. |  |

|---------------------|------------------------------------------|--|

|                     |                                          |  |

| Nom. value                                                                                                          | Details                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $f_{\rm clk} = 150  \rm MHz$                                                                                        | 1 x TMS320C2834X                                                                                                                                                                                                       |

| $f_{ m s} = 48   m kHz$<br>$R_{ m th} = 0.9   m K/W$                                                                | $12~x$ Infineon SiC IMZ120R030M1H $30~m\Omega$ $1.2~kV$ (unfolder and HF bridge-leg) $3~x$ Fischer Elektronik LAM 4 75 12                                                                                              |

| $L = 600  \mu \mathrm{H}$<br>$C_{\mathrm{dc,LF}} = 240  \mu \mathrm{F}$<br>$C_{\mathrm{dc,HF}} = 1  \mu \mathrm{F}$ | 3 x Changsung magnetic powder core LHEQ3626, 66 turns of $0.3\mathrm{mm}$ flat wire 6 x Kemet C4AQJBW5400M3LJ 40 $\mu\mathrm{F}$ , 700 V 2 x TDK Ceralink, $0.5\mu\mathrm{F}$ , 700 V                                  |

| $C_{ m ac}=4 m \mu F$                                                                                               | 4 x WE FTX2 890324026027, 1 $\mu F, 275  V_{\rm RMS}$                                                                                                                                                                  |

| $R_{ m load} = 80 \Omega$<br>$R_{ m load} = 245 \Omega$                                                             | Y-configuration (see <b>Fig. 3(a</b> ))<br>Δ-configuration (see <b>Fig. 3(e</b> ))                                                                                                                                     |

|                                                                                                                     | $f_{ m clk} = 150   m MHz$ $f_{ m s} = 48   m kHz$ $R_{ m th} = 0.9   m K/W$ $L = 600   m \mu H$ $C_{ m dc, LF} = 240   m \mu F$ $C_{ m dc, HF} = 1   m \mu F$ $C_{ m ac} = 4   m \mu F$ $R_{ m load} = 80   m \Omega$ |

Fig. 5. Phase-modular three-phase PFC rectifier hardware prototype which can be configured for Y- and  $\Delta$ -connected operation of the modules as highlighted in Fig. 3. The system dimensions are  $395 \, \mathrm{mm} \times 125 \, \mathrm{mm} \times 50 \, \mathrm{mm}$  ( $15.6 \, \mathrm{in} \times 4.9 \, \mathrm{in} \times 2.0 \, \mathrm{in}$ ) and details on the main power components are listed in Tab. 2.

not impacted by the injected CM voltage and remains fully sinusoidal and in phase with the grid voltage  $u_{\rm a}$ . At the same time, the energy buffered by the dc-link  $\Delta E_{\rm dc,a}$  is reduced by  $19.2\,\%$  for  $M_3=0.2$  and by  $31.2\,\%$  for  $M_3=0.4$  (see **Tab. 3**), and again closely matches the theoretical predictions of **Section II-A2**.

As highlighted in Fig. 6(c.ii) with (\*) the dc-link volt-

age margin for current controllability (2) reduces to  $58 \, \mathrm{V}$  for  $M_3 = 0.4$ , and for the given dc-link capacitor value  $C_{\mathrm{dc}} = 240 \, \mu\mathrm{F}$  a further increase of the harmonic injection to  $M_3 = 0.6$  would require an elevated average dc-link voltage  $> 400 \, \mathrm{V}$  which is typically undesirable as this measure would inhibit the use of  $600 \, \mathrm{V}$  Gallium Nitride (GaN) power semiconductors with superior performance compared to devices of higher blocking voltage.

Alternatively, the  $3^{\rm rd}$ -harmonic phase  $\varphi_3$  can be utilized to separate in time the maxima of the LF module input voltage  $\bar{u}_{\bar{a}\bar{N}}$  and the minima of the dc-link voltage  $U_{\rm dc,a}$  [1] such that the current controllability constraint (2) is respected. Fig. 7(a) presents experimental waveforms for a modulation index of  $M_3=0.6$  and  $\varphi_{\rm CM}=11.4^\circ$ , where a minimum dc-link voltage margin of  $20\,{\rm V}$  (highlighted with (\*)) is respected.

**Fig. 7(b)** and **(c)** further depict experimental waveforms for SVM operation with  $M_{\rm SVM}=0.5$  and  $M_{\rm SVM}=1$ , respectively. Again, the input current is not impacted by the injected CM voltage which now contains additional frequency components compared to 3<sup>rd</sup>-harmonic voltage injection. As discussed in **Section II-A3**, the reduction of the dc-link voltage fluctuation  $\Delta U_{\rm dc,a}$  and the buffered energy  $\Delta E_{\rm dc,a}$  is almost identical for  $M_{\rm SVM}=0.5$  and  $M_3=0.2$ , and for  $M_{\rm SVM}=1$  and  $M_3=0.4$  with the main advantage of the SVM operation given by the fact that no PLL is required to generate the CM voltage reference.

TABLE 3: MEASUREMENT RESULTS FOR Y-CONFIGURATION.

| Modulation                                                             | $\Delta U_{ m dc}$ calc.   | $\Delta U_{ m dc}$ meas.   | $\Delta E_{ m dc}$ calc.   | $\Delta E_{ m dc}$ meas.                              | THD meas.             | $\eta$ meas.               |

|------------------------------------------------------------------------|----------------------------|----------------------------|----------------------------|-------------------------------------------------------|-----------------------|----------------------------|

| $M_3 = 0 \text{ (conv.)}$                                              | 66.8 V                     | 66.8 V                     | 6.40 J                     | 6.47 J (100 %)                                        | 1.39%                 | 98.6%                      |

| $M_3 = 0.2$<br>$M_3 = 0.4$<br>$M_3 = 0.6$ , $\varphi_3 = 11.4^{\circ}$ | 55.0 V<br>46.6 V<br>41.0 V | 55.4 V<br>46.7 V<br>43.6 V | 5.27 J<br>4.47 J<br>3.94 J | 5.23 J (80.8 %)<br>4.45 J (68.8 %)<br>4.03 J (62.3 %) | 1.23% $1.64%$ $2.51%$ | 98.6 %<br>98.7 %<br>98.5 % |

| $\overline{M_{\rm SVM}} = 0.5$ $M_{\rm SVM} = 1.0$                     | 54.3 V<br>45.8 V           | 54.7 V<br>46.3 V           | 5.20 J<br>4.39 J           | 5.17 J (79.9 %)<br>4.38 J (67.7 %)                    | 1.17% $1.50%$         | $98.6\% \\ 98.6\%$         |

Fig. 6. Experimental waveforms for nominal power operation in Y-configuration: (a.i)-(c.i) Input voltages  $\bar{u}_{\bar{a}\bar{N}}$ ,  $\bar{u}_{\bar{c}\bar{N}}$ , CM voltage  $\bar{u}_{\rm CM}$  and input current  $\bar{i}_{a}$  for a 3<sup>rd</sup> harmonic modulation index of (a.i)  $M_{3}=0$ , (b.i)  $M_{3}=0.2$  and (c.i)  $M_{3}=0.4$  in Y-configuration. (a.ii)-(c.ii) Input voltage  $\bar{u}_{\bar{a}\bar{N}}$ , input current  $\bar{i}_{a}$ , dc-link voltage  $U_{\rm dc,a}$  and dc-link voltage variation  $\Delta U_{\rm dc,a}$  for a 3<sup>rd</sup> harmonic modulation index of (a.ii)  $M_{3}=0$ , (b.ii)  $M_{3}=0.2$  and (c.ii)  $M_{3}=0.4$  in Y-configuration. (\*) The minimum dc-link voltage margin for current controllability of 58 V within a mains period is highlighted in (c.ii).

Fig. 7. Experimental waveforms for nominal power operation in Y-configuration: (a.i-c.i) Input voltages  $u_{\bar{a}\bar{N}}, u_{\bar{c}\bar{N}}, u_{\bar{c}\bar{N}}$ , CM voltage  $u_{cm}$  and input current  $\bar{i}_a$  for a 3<sup>rd</sup> harmonic modulation index of (a.i)  $M_3 = 0.6$  and  $\varphi_{CM} = 11.4^{\circ}$ , (b.i) SVM of  $M_{SVM} = 0.5$  and (c.i) SVM of  $M_{SVM} = 1$  in Y-configuration. (a.ii-c.ii) Input voltages  $u_{\bar{a}\bar{N}}$ , input current  $\bar{i}_a$ , dc-link voltage  $U_{dc,a}$  and dc-link ripple voltage  $\Delta U_{dc,a}$  for a 3<sup>rd</sup> harmonic modulation index of (a.ii)  $M_3 = 0.6$  and  $\varphi_3 = 11.4^{\circ}$ , (b.ii) SVM of  $M_{SVM} = 0.5$  and (c.ii) SVM of  $M_{SVM} = 1$  in Y-configuration. (\*) The minimum dc-link voltage margin for current controllability of 20 V within a mains period is highlighted in (a.ii).

In summary, it can be stated that the predicted energy buffering and/or dc-link voltage fluctuation with harmonic voltage injection is verified with the prototype system (see **Tab. 3**). Alternatively, the dc-link voltage fluctuation can be kept constant for a reduced dc-link capacitor value by means of harmonic voltage injection. Note that **Tab. 3** also provides

the measured grid current Total Harmonic Distortion (THD) and electrically measured conversion efficiency  $\eta$  where the harmonic injection has only a marginal impact on both performance metrics.

# III. DELTA-CONNECTED PHASE-MODULAR CONVERTER

### A. THEORY

The three single-phase-phase isolated PFC modules in  $\Delta$ -configuration are shown in **Fig. 3(e)** with the grid voltage and current amplitude defined in **Tab. 1**. Here the modules are subject to the grid line-to-line voltages  $u_{jk}$  and currents  $i_{jk}$  which are defined as

$$u_{jk}(t) = \sqrt{3}\hat{U}_{ac}\sin(\omega_{ac}t + \phi_{jk}),$$

$$i_{jk}(t) = \frac{1}{\sqrt{3}}\hat{I}_{ac}\sin(\omega_{ac}t + \phi_{jk}),$$

(17)

with  $j,k\in\{a,b,c\}$  and  $j\neq k$ , and phase angles  $\phi_{\rm ab}=0,\phi_{\rm bc}=-\frac{2\pi}{3},\,\phi_{\rm ca}=-\frac{4\pi}{3}.$  Hence, the nominal module current in **Tab. 1** is advantageously reduced compared to Y-configuration. This, however, comes at the cost of an increased dc-link voltage with typically  $U_{\rm dc}=700\,{\rm V}$ , such that  $900\,{\rm V}$  SiC and  $900\,{\rm V}$  Silicon (Si) Super Junction (SJ) MOSFETs must be employed in the HF and unfolder bridgelegs of the converter modules, respectively. Compared to a standard monolithic boost-type three-phase PFC rectifier system [2] of the same power rating, the three single-phase PFC rectifier modules in  $\Delta$ -configuration advantageously operate with reduced input currents amplitude and rms values.

The ac-side equivalent circuit from [1] for the  $\Delta$ -configuration of the converter modules is shown in **Fig. 3(f)**. There the rectifier front-end switch-node voltages are decomposed into DM/CM and LF/HF components, e.g., for phase module a the switch-node voltage  $u_{\bar{a}b}$  is represented by

- the HF DM and CM voltage  $u_{\bar{a}b\sim}$ ,

- the LF DM voltage  $\bar{u}_{\bar{a}b} \approx u_{ab}$ .

Note that in order to avoid LF grid current distortions, the rectifier front-end switch-node voltages must not generate an LF CM voltage component, as the modules directly connect to the grid line-to-line voltages.

However, in  $\Delta$ -configuration three-phase grid currents  $i_{\rm a}, i_{\rm b}, i_{\rm c}$  are formed by subtracting the line-to-line currents  $i_{\rm ab}, i_{\rm bc}, i_{\rm ca}$  and accordingly a CM current  $i_{\rm CM}$  can circulate in the  $\Delta$ -connection and/or flow between the three single-phase PFC rectifier modules in **Fig. 3(e)** [35] [36] [37]. Hence, the module input current  $i_{\bar{1}}$  can be decomposed into

- the HF DM input current  $i_{\bar{\mathbf{a}}\sim}$ ,

- the LF DM input current  $\bar{i}_{\bar{a}b} \approx i_{ab}$ ,

- the HF CM input current  $i_{\rm CM}$ ,

- the LF CM input current  $\bar{i}_{\rm CM}$ ,

and accordingly, the LF module input power  $\bar{p}_{\rm a}$  is defined by the LF DM voltage  $\bar{u}_{\rm \bar{a}b}$  and the corresponding LF module current  $\bar{i}_{\bar{a}}$  as

$$\bar{p}_{a}(t) = \bar{u}_{\bar{a}b}(t) \cdot \bar{i}_{\bar{a}}(t) = \bar{u}_{\bar{a}b}(t) \cdot (\bar{i}_{\bar{a}b}(t) + \bar{i}_{CM}(t)).$$

(18)

Hence, the module input power can be – similar to Y-configuration – impacted by means of harmonic injection, however, here with a CM / zero-sequence current  $\bar{i}_{\rm CM}$

### 1) Conventional Modulation

The main ac-side terminal voltage waveforms for conventional modulation (i.e., with  $\bar{i}_{\rm CM}=0$ ) are presented in Fig. 3(g.i),(h.i) where the LF module input power  $\bar{p}_{\rm a}$  according to (18) is equivalent to (5) and comprises the well known twice-mains-frequency single-phase grid power pulsation on top of the (assuming ideally lossless power conversion) constant module output power  $P_{\rm a}=\frac{1}{2}\hat{U}_{\rm ac}\hat{I}_{\rm ac}$ . Similarly, the dclink capacitor  $C_{\rm dc}$  energy balance  $E_{\rm dc,a}(t)$  is defined by (6), and the dc-link LF energy buffering requirement  $\Delta E_{\rm dc,a}$  (highlighted with light-gray areas in Fig. 3(h.i)) by (7). Last, the time-varying dc-link voltage  $U_{\rm dc,a}(t)$  and the peak-to-peak dc-link LF voltage fluctuation  $\Delta U_{\rm dc,a}$  are described by (8) and (9), respectively.

In the following, the voltage  $\bar{u}_{\rm CM}$  is used to adjust the LF module input power  $\bar{p}_{\rm a}$  such that the energy buffering requirement  $\Delta E_{\rm dc,a}$  and the fluctuation of the dc-link voltage  $\Delta U_{\rm dc,a}$  is reduced.

### 2) 3<sup>rd</sup>-Harmonic CM Current Injection

In case of 3<sup>rd</sup>-harmonic current injection, the LF CM current reference value is defined as

$$i_{\rm CM}(t) = M_3 \frac{1}{\sqrt{3}} \hat{I}_{\rm ac} \sin(3\omega_{\rm ac}t), \tag{19}$$

with the  $3^{\rm rd}$ -harmonic modulation index  $M_3 = \hat{I}_{\rm CM}/(\sqrt{3}\hat{I}_{\rm ac})$ . Note that in contrast to  $3^{\rm rd}$ -harmonic voltage injection, here, the selected value of  $M_3$  has (in first approximation) no impact on the current controllability dc-link voltage margin (cf., (10)), such that no phase-shift angle (i.e.,  $\varphi_3 = 0$ ) is considered here. In **Fig. 3(g.ii,h.ii**) the characteristic waveforms of module a are illustrated for a  $3^{\rm rd}$ -harmonic current injection with  $M_3 = 0.4$ . There, the LF module input power  $\bar{p}_a$  according to (18) is described by (11) and with increasing values of  $M_3$  the twice-mains frequency power pulsation is shifted from  $2f_{\rm ac}$  to  $4f_{\rm ac}$ .

Again, the equations describing the dc-link energy and voltage waveform are (with the selected definition of the harmonic injection current (19)) equivalent to  $3^{\rm rd}$ -harmonic voltage injection, i.e., the dc-link capacitors  $C_{\rm dc}$  energy balance  $E_{\rm dc,a}(t)$  is defined by (13) and the time-varying dc-link voltage  $U_{\rm dc,a}(t)$  by (14). The numerically calculated dc-link LF energy buffering requirement  $\Delta E_{\rm dc,a}$  and the peak-to-peak dc-link LF voltage fluctuation  $\Delta U_{\rm dc,a}$  are provided in Tab. 4. Note that for a given value of  $M_3$ ,  $\Delta E_{\rm dc,a}$  is identical for CM voltage injection (Y-configuration) and CM current injection ( $\Delta$ -configuration), whereas  $\Delta U_{\rm dc,a}$  is reduced in  $\Delta$ -configuration due to the elevated average dc-link voltage  $U_{\rm dc}$  (cf., Tab. 3, Tab. 4).

### B. CONTROL CONCEPT

The considered control concept presented in **Fig. 4** is similar to the Y-configuration (see **Sec. II-B**) and comprises the outer, low-bandwidth dc-link voltage controller (for all three converter modules) and the underlying current controllers. In

**Fig. 8.** Block diagram of a cascaded control of the PFC rectifier input stages of **Fig. 3(e)** considering a  $3^{\rm rd}$  harmonic CM current injection  $\bar{i}_{\rm CM}^*$ .

contrast to Y-configuration, the module input currents in  $\Delta$ -configuration no longer sum to zero and therefore three individual current controllers are required to ensure sinusoidal currents in all phases. Here the  $3^{rd}$ -harmonic CM current reference is added to the sinusoidal DM reference current values, i.e., the CM current reference is actively tracked by

the current controllers.

### C. EXPERIMENTAL RESULTS

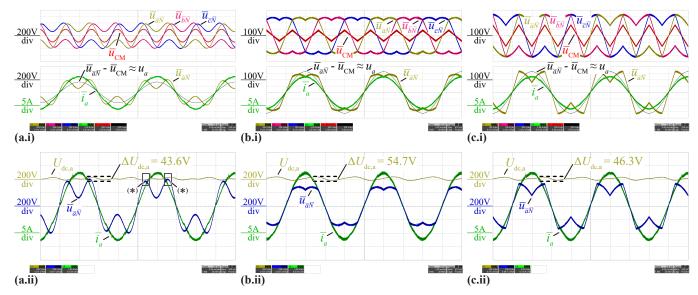

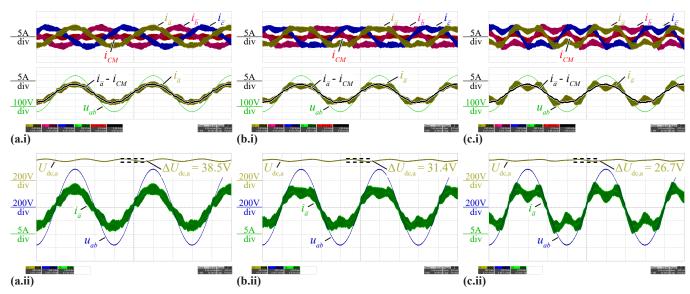

Here, the hardware demonstrator of **Fig. 5** is reconfigured to a  $\Delta$ -arrangement of the three single-phase PFC rectifier modules. Measurement results for nominal power operation are presented in **Fig. 9**. In case of conventional modulation (see **Section III-A1**) the CM current is set to  $\bar{i}_{\rm CM} \approx 0$  and the module input currents  $i_{\bar{i}}$  in **Fig. 9(a.i)** are (apart from the HF current ripple) fully sinusoidal and in phase with the respective grid line-to-line voltage. **Fig. 9(a.ii)** further depicts the dc-link voltage of module a,  $U_{\rm dc,a}$ , and the peak-to-peak dc-link voltage fluctuation results to  $\Delta U_{\rm dc} = 38.5\,{\rm V}$  corresponding to a buffered energy  $\Delta E_{\rm dc} = 6.6\,{\rm J}$  (obtained by integrating the measured voltage  $\bar{u}_{\bar{a}b}$  and current  $\bar{i}_{\bar{a}}$ ) which closely match the calculated values according to (9) and (7) provided in **Tab. 4**.

Next, operation with a  $3^{\text{rd}}$ -harmonic current injection index  $M_3 = 0.2$  and  $M_3 = 0.4$  is depicted in **Fig. 9(b)** and **(c)**, respectively. There, the module the module input currents  $i_{\bar{i}}$  comprise an increasing CM component, and the

Fig. 9. Experimental waveforms for nominal power operation in  $\Delta$ -configuration: (a.i-c.i) Module input currents  $i_{\bar{a}}$ ,  $i_{\bar{b}}$ ,  $i_{\bar{c}}$ , CM current  $i_{CM}$  and grid line-to-line voltage  $u_{ab}$  for a 3<sup>rd</sup> harmonic modulation index of (a.i)  $M_3 = 0$ , (b.i)  $M_3 = 0.2$  and (c.i)  $M_3 = 0.4$ . The sinusoidal LF DM current  $i_{\bar{a}} - i_{CM}$  was extracted from the exported oscilloscope waveforms and added on top of the screenshots for illustration purposes. (a.ii-c.ii) Module input current  $i_{\bar{a}}$ , grid line-to-line voltage  $u_{ab}$ , dc-link voltage  $U_{dc,a}$  and dc-link ripple voltage  $\Delta U_{dc,a}$  for a 3<sup>rd</sup> harmonic modulation index of (a.ii)  $M_3 = 0$ , (b.ii)  $M_3 = 0.2$  and (c.ii)  $M_3 = 0.4$ .

**TABLE 4:** MEASUREMENT RESULTS FOR Δ-CONFIGURATION COMPROMISING THE DC-LINK VOLTAGE RIPPLE AND THE ENERGY STORED IN THE DC-LINK CAPACITORS

| Modulation                 | $\Delta U_{ m dc}$ calc. | $\Delta U_{ m dc}$ meas. | $\Delta E_{ m dc}$ calc. | $\Delta E_{ m dc}$ meas.           | THD meas.     | $\eta$ meas.       |

|----------------------------|--------------------------|--------------------------|--------------------------|------------------------------------|---------------|--------------------|

| $M_3 = 0$ (conv.)          | $38.1\mathrm{V}$         | $38.5\mathrm{V}$         | $6.40\mathrm{J}$         | 6.60 J (100 %)                     | 4.70%         | 99.2%              |

| $M_3 = 0.2$<br>$M_3 = 0.4$ | 31.4 V<br>26.6 V         | 31.4 V<br>26.7 V         | 5.27 J<br>4.47 J         | 5.37 J (81.4 %)<br>4.64 J (70.3 %) | 4.87% $4.72%$ | $99.0\% \\ 99.0\%$ |

grid current remains fully sinusoidal. At the same time, the dc-link voltage variation  $\Delta U_{\rm dc,a}$  is reduced by  $18.6\,\%$  for  $M_3=0.2$  and by  $29.7\,\%$  for  $M_3=0.4$ , thereby verifying the predicted energy buffering and/or dc-link voltage fluctuation with harmonic current injection (see **Tab. 4**).

Here, in contrast to harmonic voltage injection, the current controllability is not affected by injected CM current. However, the module input current rms stresses increase with  $M_3$ , thereby causing additional conduction losses. Hence, the measured converter efficiency drops from  $\eta=99.2\,\%$  to  $\eta=99.0\,\%$  for the considered operating point. Note that the improved conversion efficiency in  $\Delta$ -configuration compared to Y-configuration results as a  $700\,\mathrm{V}$  dc-link better utilizes the employed  $1200\,\mathrm{V}$  SiC MOSFETs of the hardware demonstrator and does not indicate a general superiority of the  $\Delta$ -configuration over the Y-configuration.

### IV. CONCLUSION

Phase-modular isolated three-phase Power Factor Correction (PFC) rectifiers comprising three front-end single-phase PFC rectifier modules show superior conversion efficiency compared to a standard monolithic three-phase rectifier system due to the lower dc-link voltage level and/or reduced current stresses of the power semiconductors. Further, reconfiguration from a star (Y)-arrangement to a delta ( $\Delta$ )-arrangement of the PFC rectifier modules allows for wide input voltage ranges without compulsory over dimensioning of the main power components. However, each of the front-end single-phase PFC rectifier modules requires a large dc-link capacitor to buffer the single-phase twice-mains-frequency input power pulsation.

Recent literature proposes a power pulsation reduction by means of harmonic injection techniques and this paper provides an experimental verification of the proposed modulation concept. Both a Y-arrangement (i.e., with CM voltage injection, see **Fig. 3(a)**) and a  $\Delta$ -arrangement (i.e., with CM current injection, see **Fig. 3(e)**) of the three front-end single-phase PFC rectifier modules is considered. Measurement results obtained from a  $6\,\mathrm{kW}$  prototype reveal a dc-link voltage variation and/or energy buffering reduction by up to  $38.6\,\%$  enabled by the harmonic injection modulation compared to conventional operation, which is in line with the theoretical considerations.

In closing it is important to highlight, that future research could also investigate advanced modulation strategies to further minimize the dc-link energy buffering requirement and/or minimize the switching losses by means of clamping modulation [38], [39].

### **REFERENCES**

- [1] D. Menzi, J. W. Kolar, J. A. Anderson, and M. J. Kasper, "New third-harmonic injection modulation reducing the dc-link energy buffer requirement of phase-modular three-phase isolated PFC AC/DC converter systems," in Proc. of the IEEE Workshop on Control and Modelling of Power Electronics (COMPEL), 2021, pp. 1–7.

- [2] J. W. Kolar and T. Friedli, "The essence of three-phase PFC rectifier systems—Part I," IEEE Transactions on Power Electronics, vol. 28, no. 1, pp. 176–198, Jan. 2013.

- [3] G. Buticchi, L. Costa, and M. Liserre, "Improving system efficiency for the more electric aircraft," IEEE Industrial Electronics Magazine, vol. 11, no. 3, pp. 26–36, 2017.

- [4] T. Guillod, D. Rothmund, and J. W. Kolar, "Active magnetizing current splitting ZVS modulation of a 7 kV/400 V DC Transformer," IEEE Trans. Power Electron., vol. 35, no. 2, pp. 1293–1305, 2020.

- [5] I. Takahashi and Y. Itoh, "Electrolytic Capacitor Less PWM Inverter," in Proc. of the IEEE International Power Electronics Conference (IPEC, ECCE Asia), 1990, pp. 131–138.

- [6] I. Takahashi, I. Ando, Y. Ito, and K. Amei, "Development of a long-life three-phase flywheel UPS using an electrolytic capacitorless converter/inverter," Electrical Engineering in Japan, vol. 127, no. 3, pp. 25–32, 1999

- [7] M. Schweizer, T. Friedli, and J. W. Kolar, "Comparison and implementation of a 3-level NPC voltage link back-to-back converter with SiC and Si diodes," in Proc. of the IEEE Applied Power Electronics Conference and Exposition (APEC), Feb. 2010, pp. 1527–1533.

- [8] J. Kolar, R. Wieser, and H. Ertl, "Analysis of a wide speed range starter/alternator system based on a novel converter topology for series/parallel stator winding configuration," in Proc. of the IEEE Industry Applications Society Annual Meeting (IAS), vol. 4. Phoenix, AZ, USA: IEEE, 1999, pp. 2631–2641.

- [9] P. Sun, L. Zhou, and K. M. Smedley, "A reconfigurable structure DC–DC converter with wide output range and constant peak power," IEEE Transactions on Power Electronics, vol. 26, no. 10, pp. 2925–2935, Oct. 2011.

- [10] M. Chen, K. K. Afridi, and D. J. Perreault, "Stacked switched capacitor energy buffer architecture," IEEE Transactions on Power Electronics, vol. 28, no. 11, pp. 5183–5195, Nov. 2013.

- [11] D. Chapman, D. James, and C. Tuck, "A high density 48 V 200 A rectifier with power factor correction - An engineering overview," in Proc. of the International Telecommunications Energy Conference (INTELEC), vol. 1, 1993, pp. 118–125.

- [12] R. Greul, S. D. Round, and J. W. Kolar, "Analysis and control of a three-phase, unity power factor Y-rectifier," IEEE Transactions on Power Electronics, vol. 22, no. 5, pp. 1900–1911, Sept. 2007.

- [13] A. Singh, A. Mallik, and A. Khaligh, "A comparative study of failure-tolerant three-phase RTRUs for more electric aircrafts," in Proc. of the IEEE Applied Power Electronics Conference and Exposition (APEC), 2019, pp. 1121–1127.

- [14] F. Vollmaier, A. Connaughton, T. Langbauer, and K. Krischan, "Exploiting a multi-port transformer for minimal DC-link capacitance for an automotive onboard charger," in Proc. of the European Conference on Power Electronics and Applications (ECCE Europe), 2020, pp. 1–8.

- [15] F. Vollmaier, A. Connaughton, I. Recepi, T. Langbauer, M. Pajnic, W. Konrad, and C. Mentin, "Tiny power box-Exploiting multiport series resonant topologies for very high power density onboard chargers," in Proc. of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management (PCIM Europe). VDE, 2022, pp. 1–9.

- [16] P. Ide, F. Schafmeister, J. Richterm, B. Pour, D. Spesser, and D. Herke, "Adaptable rectifier arrangement for operation with different AC grids," 2013, European Patent Application EP2869445-A1.

- [17] J. Azurza Anderson, G. Zulauf, P. Papamanolis, S. Hobi, S. Mirić, and J. W. Kolar, "Three levels are not enough: Scaling laws for multilevel converters in AC/DC applications," IEEE Transactions on Power Electronics, vol. 36, no. 4, pp. 3967–3986, 2021.

- [18] TDK Electronics AG, Aluminum Electrolytic Capacitors: General technical information, App. Note, 2019. [Online]. Available: https://www.tdk-electronics.tdk.com

- [19] Nippon Chemi-Con, Judicious use of aluminum electrolytic capacitor, Technical Note, CAT. No. E1001U. [Online]. Available: https://chemi-con. com/wp-content/uploads/2021/04/Technical-Notes.pdf

- [20] M. Chen, K. K. Afridi, and D. J. Perreault, "Stacked switched capacitor energy buffer architecture," IEEE Transactions on Power Electronics, vol. 28, no. 11, pp. 5183–5195, 2013.

- [21] D. Neumayr, D. Bortis, J. W. Kolar, M. Koini, and J. Konrad, "Comprehensive large-signal performance analysis of ceramic capacitors for power pulsation buffers," in Proc. of the IEEE Workshop on Control and Modeling for Power Electronics (COMPEL), 2016, pp. 1–8.

- [22] Z. Liao and R. C. N. Pilawa-Podgurski, "Power harmonic elimination technique for using non-linear ceramic capacitors under large voltage swings for single-phase active power decoupling," in Proc. of the IEEE Workshop on Control and Modeling for Power Electronics (COMPEL), Nov. 2020, pp. 1–7.

- [23] H. Kim, J. Park, S. Kim, R. M. Hakim, H. Belkamel, and S. Choi, "A single-stage electrolytic capacitor-less EV charger with single-and threephase compatibility," IEEE Transactions on Power Electronics, vol. 37, no. 6, pp. 6780–6791, 2021.

- [24] A. J. Hanson, A. F. Martin, and D. J. Perreault, "Energy and size reduction of grid-interfaced energy buffers through line waveform control," IEEE Transactions on Power Electronics, vol. 34, no. 11, pp. 11442–11453, Nov. 2019.

- [25] S. Kampl and R. Garcia, "2500 W full-bridge totem-pole power factor correction using CoolGaN<sup>TM</sup>," Infineon Technol. AG, Munich, Germany, Tech. Rep. AN\_201702\_PL52\_011, 2018.

- [26] X. Gong, G. Wang, and M. Bhardwaj, "6.6kW three-phase interleaved totem pole PFC design with 98.9% peak efficiency for HEV/EV onboard charger," in Proc. of the IEEE Applied Power Electronics Conference and Exposition (APEC), 2019, pp. 2029–2034.

- [27] G. Buja and G. Indri, "Improvement of pulse width modulation techniques," Archiv für Elektrotechnik, vol. 57, no. 5, pp. 281–289, Sept. 1975.

- [28] Z. Li, R. Lizana, Z. Yu, S. Sha, A. V. Peterchev, and S. M. Goetz, "Modulation and control of series/parallel module for ripple-current reduction in star-configured split-battery applications," IEEE Transactions on Power Electronics, vol. 35, no. 12, pp. 12977–12987, Dec. 2020.

- [29] A. Marcos-Pastor, E. Vidal-Idiarte, A. Cid-Pastor, and L. Martínez-Salamero, "Minimum DC-link capacitance for single-phase applications with power factor correction," IEEE Transactions on Industrial Electronics, vol. 67, no. 6, pp. 5204–5208, June 2020.

- [30] P. Cortes, J. Huber, M. Silva, and J. W. Kolar, "New modulation and control scheme for phase-modular isolated matrix-type three-phase AC/DC converter," in Proc. of the Annual Conference of the IEEE Industrial Electronics Society (IECON), Nov. 2013, pp. 4899–4906.

- [31] J. W. Kolar, "Control strategy for balancing the DC output voltages of star connected single phase PWM rectifiers (in German – Vorrichtung zur Regelung der Phasenzwischenkreisspannungen einer Sternschaltung einphasiger Pulsgleichrichtersysteme in Analogie zu Dreiphasen-DreipunktPulsgleichrichtersystemen)," 2006, Swiss Patent CH699822-B1.

- [32] J. Biela, U. Drofenik, F. Krenn, J. Miniboeck, and J. W. Kolar, "Three-phase Y-rectifier cyclic 2 out of 3 DC output voltage balancing control method," IEEE Transactions on Power Electronics, vol. 24, no. 1, pp. 34–44, 2009.

- [33] M. Boyra and J.-L. Thomas, "A review on synchronization methods for grid-connected three-phase VSC under unbalanced and distorted conditions," in Pro. of the IEEE European conference on Power Electronics and Applications (EPE ECCE Europe), 2011, pp. 1–10.

- [34] Infineon Technologies AG, "IMZ120R030M1H." [Online]. Available: https://www.infineon.com/cms/en/product/power/mosfet/ silicon-carbide/discretes/imz120r030m1h/

- [35] M. J. Kocher and R. L. Steigerwald, "An AC-to-DC converter with high quality input waveforms," IEEE Transactions on Industry Applications, vol. IA-19, no. 4, pp. 586–599, Jul. 1983.

- [36] R. Greul, S. D. Round, and J. W. Kolar, "The Delta-rectifier: Analysis, control and operation," IEEE Transactions on Power Electronics, vol. 21, no. 6, pp. 1637–1648, Nov. 2006.

- [37] Z. Li, R. Lizana, S. M. Lukic, A. V. Peterchev, and S. M. Goetz, "Current injection methods for ripple-current suppression in delta-configured splitbattery energy storage," IEEE Transactions on Power Electronics, vol. 34, no. 8, pp. 7411–7421, Aug. 2019.

- [38] J. W. Kolar, H. Ertl, and F. C. Zach, "Influence of the modulation method on the conduction and switching losses of a PWM converter system," IEEE Transactions on Industry Applications, vol. 27, no. 6, pp. 1063–1075, 1991.

- [39] A. M. Hava, "Carrier-based PWM-VSI drives in the overmodulation region," Ph.D. dissertation, The University of Wisconsin-Madison, USA (WI), 1998.

THOMAS LANGBAUER (S'18-M'22) received his B.Sc. in 2015 and M.Sc. degree in 2018 in electrical engineering from Graz University of Technology. Since 2018 he is working for Silicon Austria Labs within the Power Electronics Divison. He contributed to the Tiny Power Box project, which was aiming for highest power density for a bidirectional onboard charger for electric cars. From 2021 to 2022 he was an academic guest at the Power Electronic Systems Laboratory at ETH

Zurich for six months. Currently, he is finalizing his PhD thesis, which is supervised at the Electric Drives and Machines Institute at Graz University of Technology. His main research interests are charging technologies and power dense converters including modulation schemes and control design.

DAVID MENZI (M'22) received his B.Sc. and M.Sc. degree in Electrical Engineering and Information Technology at the Swiss Federal Institute of Technology (ETH), Zurich, Switzerland, in 2015 and 2017, respectively, where he focused on power electronics, control theory, and high voltage technology. He also spent a semester at the Royal Institute of Technology (KTH) in Stockholm, Sweden as an exchange student. During his studies, he worked at ABB Medium Voltage

Drives (MVD) in Turgi, Switzerland, as an intern and working student. He conducted his Ph.D. research in Electrical Engineering from 2018 to 2022 on bidirectional phase-modular three-phase buck-boost converter systems under the supervision of Prof. J.W. Kolar at the Power Electronic Systems Laboratory (PES) of ETH Zurich, where he is now working as a postdoctoral researcher.

VALENTIN MARUGG received the B.Sc. and M.Sc. degrees in electrical engineering and information technology from the Swiss Federal Institute of Technology (ETH), Zurich, Switzerland, in 2020 and 2022, respectively, where he focused on power electronics and high voltage technology. He also spent a semester with Purdue University, Indiana, USA, as an Exchange Student. During his studies, he was one year with ABB Traction, Turgi, Switzerland, as an Intern. Currently he is a

Junior R&D Engineer with ABB Traction, focusing on gate-driver development.

FRANZ VOLLMAIER received his B.Sc. degree in electrical engineering and M.Sc. degree in electrical engineering and business from Graz University of Technology in 2016. After collecting professional experience in the photovoltaic energy industry, he joined the Power Electronics Division at Silicon Austria Labs in 2018. His current research and focus of his PhD, which is supervised at the Electric Drives and Machines Institute at Graz University of Technology, is on power dense

charging topologies used for electro-mobility applications.

JON AZURZA received his B.Sc. degree in Industrial Technology Engineering from TEC-NUN School of Engineering of the University of Navarra in 2014, and his M.Sc. and Ph.D. degrees in Electrical Engineering from ETH Zurich in 2016, and 2020, respectively. During his Ph.D. studies at the Power Electronic Systems Laboratory at ETH Zurich under the supervision of Prof. J.W. Kolar he focused on ultra-high efficiency three-phase multi-level PWM converters. In 2013

and 2014 he worked for Fraunhofer IIS in Nuremberg, Germany, and as of March 2021 he is with Infineon Technologies Austria AG working on novel topology, modulation and control methods, focusing on WBG devices. He has authored and co-authored 20+ scientific publications and has several patent applications pending.

JOHANN W. KOLAR (F'10) received his M.Sc. and Ph.D. degree (summa cum laude - promotio sub auspiciis praesidentis rei publicae) from the University of Technology Vienna, Austria, in 1997 and 1999, respectively. Since 1984, he has been working as an independent researcher and international consultant in close collaboration with the Vienna University of Technology, in the fields of power electronics, industrial electronics and high performance drive systems. He was appointed As-

soc. Professor and Head of the Power Electronic Systems Laboratory at the Swiss Federal Institute of Technology (ETH) Zurich on Feb. 1, 2001, and was promoted to the rank of Full Prof. in 2004. Dr. Kolar has proposed numerous novel converter concepts incl. the Vienna Rectifier, the Sparse Matrix Converter and the Swiss Rectifier, has spearheaded the development of x-million rpm motors, and has pioneered fully automated multi-objective power electronics design procedures. He has supervised 80+ Ph.D. students to completion, has published 1000+ journal and conference papers and 4 book chapters, and has filed 200+ patents in the course of international industry research collaborations. He has presented 40+ educational seminars at leading international conferences and has served as IEEE PELS Distinguished Lecturer from 2012 - 2016. He has received 40+ IEEE Transactions and Conference Prize Paper Awards, the 2014 IEEE Power Electronics Society R. David Middlebrook Achievement Award, the 2016 IEEE PEMC Council Award, the 2016 IEEE William E. Newell Power Electronics Award, the 2021 EPE Outstanding Achievement Award and 2 ETH Zurich Golden Owl Awards for excellence in teaching. He is a Fellow of the IEEE and was elected to the U.S. National Academy of Engineering as an international member in 2021. The focus of his current research is on ultra-compact/efficient WBG converter systems, ANN-based design procedures, Solid-State Transformers, ultra-high speed drives, bearingless motors, and life cycle analysis of power electronics converter systems.

. .

MATTHIAS KASPER received the M.Sc. and Dr.Sc. degree in electrical engineering from the Swiss Federal Institute of Technology (ETH) Zurich, Switzerland, in 2011 and 2016, respectively. In his PhD at the Power Electronic Systems Laboratory at ETH Zurich he dealt with multi-cell converter systems for different applications. Since January 2017 he is part of the Systems Innovations Lab of Infineon Technologies Austria AG where he is leading a team researching novel circuit

topologies, control schemes, and multi-objective optimization routines, with a special focus on wide band-gap semiconductors. He has authored and co-authored more than 20 scientific publications and holds 12 international patents.