# Optimal Common-Mode Voltage Injection for Phase-Modular Three-Phase PFC Rectifiers Minimizing Energy Buffering Requirement

David Menzi, *Member, IEEE*, Valentin Marugg, Thomas Langbauer, *Member, IEEE*, Johann W. Kolar, *Fellow, IEEE*

Abstract-Realizing an isolated three-phase Power Factor Correction (PFC) ac-dc converter as a phase-modular system, i.e, by star-connecting three single-phase PFC rectifier frontends with individual isolated dc-dc converter stages generating a common dc output voltage advantageously facilitates the use of standard single-phase converter modules. Further the low dc-link voltage level of typically  $400\,V$  (for a grid with  $230\,V_{rms}$ line-to-neutral voltage) allows to employ high performance 600 V power semiconductors. The main drawback of this concept, however, is the fact that the time-varying single-phase input power only sums to a constant three-phase output power at the isolated dc output, such that large dc-link capacitor values are required in each module (in the range of several  $100\,\mu F$  for a  $6\,kW$  system), thereby limiting the achievable power density. It is known from literature that the dc-link energy buffering requirement  $\Delta E_{\rm dc}$  can be reduced by means of a third-harmonic common-mode (CM) voltage injection modulation and this paper identifies the optimal CM voltage waveform with respect to minimizing  $\Delta E_{\mathrm{dc}}$ , i.e., reducing  $\Delta E_{

m dc}$  to the theoretical minimum by combining a bruteforce evaluation of the time-domain CM voltage waveform with phase-symmetry considerations. Additionally, converter operation with minimum dc-link voltage and/or dc-link capacitor values is analyzed and a saturable grid current controller allowing operation of the PFC rectifier front-ends with the optimal CM voltage waveform is investigated. Experimental results with a 6kW prototype system yield a reduction in  $\Delta E_{

m dc}$  by up to 42 % (compared to conventional sinusoidal modulation), which closely matches the theoretical prediction. Also, PFC rectifier operation with a dc-link voltage level as low as 285 V (i.e., below the  $325\,V_{pk}$  grid line-to-neutral voltage amplitude) and with ultra-low dc-link capacitor values is demonstrated.

Index Terms—ac-dc converter, three-phase, PFC rectifier, modular, harmonic injection, zero sequence, CM voltage injection

### I. INTRODUCTION

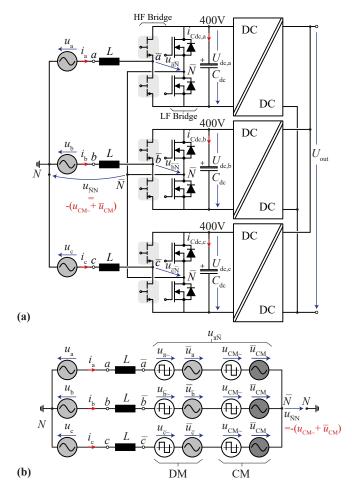

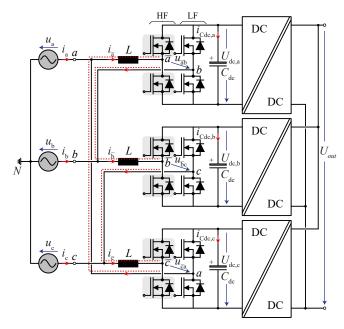

Forming a phase-modular isolated three-phase Power Factor Correction (PFC) ac-dc converter system comprising three single-phase PFC rectifier front-ends (with individual isolated dc-dc converter stages) connected to a common starpoint  $\bar{N}$  as highlighted in **Fig. 1** [1]–[5] has two major advantages: First, standard single-phase PFC rectifiers [6] can be employed, which is beneficial in terms of economies of scale, design effort, and maintainability. Second, the low average dc-link voltage level of typically  $\bar{U}_{\rm dc}=400\,{\rm V}$  (compared to a standard non-modular/monolithic PFC ac-dc converter with an 800 V dc-link and 1.2 kV Silicon Carbide (SiC) semiconductors [7]–[9]) allows the usage of superior 600 V Gallium Nitride (GaN) semiconductors and thereby enables high conversion efficiencies  $\eta>99\,\%$  even for the

This paper has **not** been previously presented at any conference or submitted for review elsewhere.

**Fig. 1.** (a) Considered converter structure of a phase-modular three-phase isolated Power Factor Correction (PFC) ac-dc converter system (main specifications are listed in **Table I**): Each phase module comprises a totem-pole PFC rectifier front-end with an HF bridge-leg and an LF unfolder bridge-leg combined with an isolated dc-dc converter stage connected to a common dc output voltage  $U_{\rm out}$ . The module starpoint  $\bar{N}$  is not connected to the grid starpoint N such that the CM voltage  $u_{\bar{N}N}$  does not drive any current in the grid [14]. (b) ac-side equivalent circuit of the system: Although the CM voltage does not impact the grid currents, the grid currents flow through the Low-Frequency (LF) Common-Mode (CM) voltage  $\bar{u}_{\rm CM}$  which hence can be used to alter the LF module input power flow.

simple two-level totem-pole PFC rectifier front-end structure considered here [6,10]–[13].

The main drawback of the concept depicted in Fig. 1, however, is given by the fact that each converter module  $x \in \{a,b,c\}$  is subject to a time-varying single-phase input power. Hence, large dc-link capacitor values  $C_{\rm dc}$  are required which limit the maximally achievable volumetric

TABLE I: SYSTEM SPECIFICATIONS.

| Design.                                                                                   | Description                                                                                                   | Value                                                                                                                                 |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| $egin{array}{c} U_{ m ac} \ I_{ m ac} \ f_{ m ac} \ P_{ m N} \ ar{U}_{ m dc} \end{array}$ | Grid voltage (line-to-neutral) Grid phase current Grid frequency Nominal system power Average dc-link voltage | $\begin{array}{l} 3\times230\mathrm{V_{rms}}\\ 3\times8.7\mathrm{A_{rms}}\\ 50\mathrm{Hz}\\ 6\mathrm{kW}\\ 400\mathrm{V} \end{array}$ |

| $f_{\rm s}$ $L$ $C_{\rm dc}$                                                              | Switching frequency<br>Boost inductor value<br>dc-link capacitor value                                        | 72 kHz<br>600 μH<br>240 μF                                                                                                            |

converter power density.

Third-harmonic CM voltage injection modulation [15] and Space Vector Modulation (SVM) [16] are known from the field of non-modular/monolithic three-phase motor drive inverter systems and allow to increase the linear voltage operating range and/or dc-link voltage utilization. It was shown in [14,17] that third-harmonic injection modulation, which results in a CM voltage  $u_{\rm CM}$  between the grid starpoint N and the module starpoint  $\bar{N}$  in **Fig. 1a**, allows to redirect the pulsating single-phase input power among the modules, where sinusoidal grid currents  $i_a, i_b, i_c$  are maintained due to the open starpoint configuration (a similar concept is also known from cascaded modular H-bridge converters [18]-[20]). Thereby, the dc-link energy buffering requirement can be reduced by up to 30% compared to conventional modulation (and up to 39 % for phase-shifted third-harmonic voltage injection) [17] and further the minimally required dclink voltage  $\bar{U}_{\rm dc}$  and/or dc-link capacitance value  $C_{\rm dc}$  can be reduced. The analysis of CM voltage injection in literature is, however, thus far limited to specific voltage waveforms (e.g., the above mentioned third-harmonic voltage injection), and this paper derives the optimum CM voltage waveform to minimize the dc-link energy buffering requirement by combining a brute-force waveform evaluation within the (time-varying) range of feasible CM voltages and phasesymmetry considerations.

This paper is structured as follows: Sec. II discusses the impact of the LF CM voltage on the PFC rectifier front-end power pulsation and identifies the optimal time-domain CM voltage waveform. Further, the lower bound of the dc-link voltage and dc-link capacitor values for the optimal CM voltage modulation is derived. Then, Sec. III presents a collaborative control structure where at any given point in time only two out of three rectifier modules are switched at High-Frequency (HF), thereby enabling PFC rectifier frontend operation with the optimal CM voltage injection modulation. Experimental results with a 6kW prototype system that verify the theoretical considerations are presented in Sec. IV and Sec. V summarizes the main findings of this paper. Additionally, **Appendix A** discusses several dc-link voltage levels and the corresponding optimal CM voltage waveforms.

#### II. OPTIMUM CM VOLTAGE INJECTION MODULATION

# A. Power Flow Fundamentals

The primary goal of the PFC rectifier front-ends in Fig. 1a (main converter waveforms are shown in Fig. 2) is to

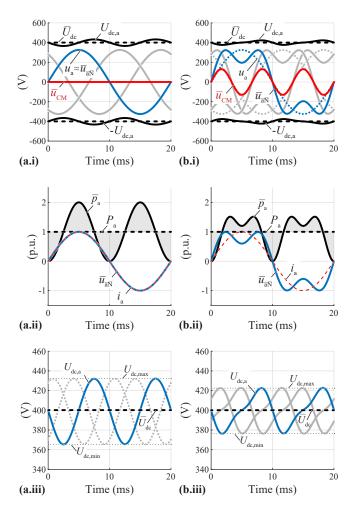

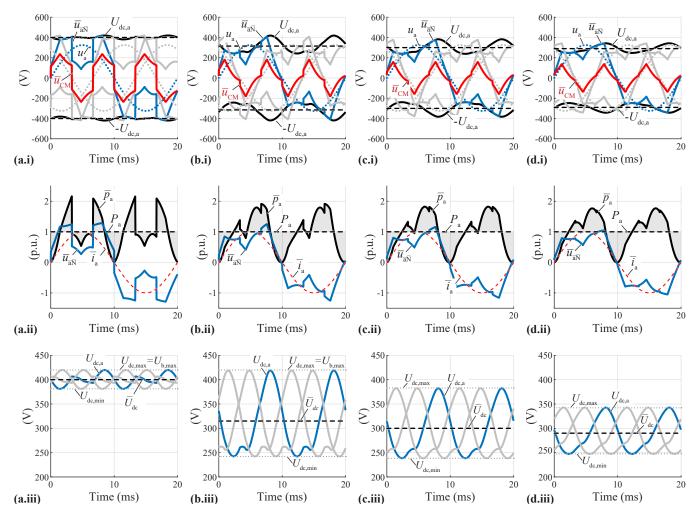

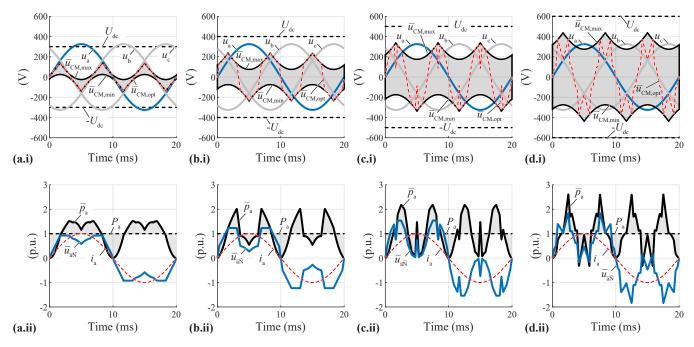

Fig. 2. Main PFC rectifier front-end waveforms (with focus on phase a) according to the system specifications in Table I for (a) conventional modulation (with  $\bar{u}_{\rm CM}=0,\,\Delta E_{\rm dc,0}=6.4\,\rm J,\,\Delta U_{\rm dc}=66.8\,\rm V)$  and (b) third-harmonic voltage injection modulation [17] (with  $\bar{u}_{\rm CM}=0.4\cdot\hat{U}_{\rm ac}\sin(3\omega_{\rm ac}t),\,\Delta E_{\rm dc}=4.5\,\rm J,\,\Delta U_{\rm dc}=46.6\,\rm V)$ : (x.i) sinusoidal grid voltages  $u_{\rm a},u_{\rm b},u_{\rm c},\,\rm LF$  PFC rectifier front-end input voltages  $\bar{u}_{\bar{\rm a}\bar{\rm N}},\bar{u}_{\bar{\rm b}\bar{\rm N}},\bar{u}_{\bar{\rm c}\bar{\rm N}}$  with respect to the common starpoint  $\bar{N}$ , and module a dc-link voltage  $U_{\rm dc,a}$  (the average value  $\bar{U}_{\rm dc}$  is represented by a dashed line). (x.ii) phase a LF PFC rectifier front-end input voltage  $\bar{u}_{\bar{\rm a}\bar{\rm N}},\,\rm grid$  current  $i_{\rm a},\,\rm and\,\,LF$  input power  $\bar{p}_{\rm a}$ . (x.iii) module dc-link voltages  $U_{\rm dc,a},\,U_{\rm dc,b},\,U_{\rm dc,c}$  and the resulting minimum  $U_{\rm dc,min},\,\rm average\,\,\bar{U}_{\rm dc}$  and maximum  $U_{\rm dc,max}$  values of the dc-link voltages.

regulate sinusoidal grid currents  $i_{\rm a}, i_{\rm b}, i_{\rm c}$  with amplitude  $\hat{I}_{\rm ac}$  and in phase with the respective grid voltages  $u_{\rm a}, u_{\rm b}, u_{\rm c}$  with amplitude  $\hat{U}_{\rm ac}$ . The grid power of phase  $x \in \{a,b,c\}$  is defined as

$$p_{\rm g,x}(t) = u_{\rm x} \cdot i_{\rm x} = \underbrace{\frac{1}{2} \hat{U}_{\rm ac} \hat{I}_{\rm ac}}_{P_{\rm g,x}} - \underbrace{\frac{1}{2} \hat{U}_{\rm ac} \hat{I}_{\rm ac} \cos(2\omega_{\rm ac}t + 2\phi_{\rm x})}_{p_{\rm g,x\sim}(t)},$$

(1)

with the phase angles  $\phi_{\rm x}=\{0,-120^\circ,-240^\circ\}$ , and comprises an ac component  $p_{\rm g,x\sim}$  at twice the grid angular frequency  $\omega_{\rm ac}=2\pi f_{\rm ac}$  on top of the average phase input power  $P_{\rm g,x}=\frac{1}{3}P_{\rm N}$ , with  $P_{\rm N}$  the nominal system power.

**Fig. 1b** depicts the ac-side equivalent circuit of the system. The module starpoint  $\bar{N}$  is not connected to the grid starpoint N and therefore the CM voltage  $u_{\bar{N}N}$  (comprising an HF component  $u_{\rm CM}$ ) and an LF component  $\bar{u}_{\rm CM}$ ) does not drive any current. However, the grid phase currents flow through

the LF CM voltage  $\bar{u}_{\rm CM}$  in each module which thereby impacts the LF input power of module x as

$$\bar{p}_{x}(t) = \bar{u}_{\bar{x}\bar{N}}(t) \cdot i_{x}(t) = (u_{x}(t) + \bar{u}_{CM}(t)) \cdot i_{x}(t).$$

(2)

For a constant PFC rectifier front-end dc output power  $P_{\rm x}=P_{\rm g,x}$  (assuming a lossless power conversion) the energy buffered by the dc-link capacitor  $C_{\rm dc}$  of module x is defined as

$$E_{\rm dc,x}(t) = \int_0^t (\bar{p}_{\rm x}(\tau) - P_{\rm x}) d\tau. \tag{3}$$

With  $\Delta E_{\rm dc} = {\rm max}(E_{\rm dc,x}(t)) - {\rm min}(E_{\rm dc,x}(t))$  as energy buffering requirement of the dc-link capacitors  $C_{\rm dc}$ , and the LF peak-to-peak voltage fluctuation of the dc-link capacitors results to

$$\Delta U_{\rm dc} = \frac{\Delta E_{\rm dc}}{C_{\rm dc}\bar{U}_{\rm dc}}.\tag{4}$$

**Fig. 2a** depicts the main converter waveforms of the module a for conventional operation with  $\bar{u}_{\rm CM}=0$  such that the module power  $\bar{p}_{\rm x}(t)\approx p_{\rm g,x}(t)$  (see **Fig. 2a.ii**) shows the characteristic twice-mains-frequency single-phase grid variation. Here, the energy buffering requirement (highlighted by a gray area) results to

$$\Delta E_{\rm dc,0} = \frac{\frac{1}{2}\hat{U}_{\rm ac}\hat{I}_{\rm ac}}{2\pi f_{\rm ac}},\tag{5}$$

with  $\Delta E_{\mathrm{dc,0}} = 6.4\,\mathrm{J}$  for the specifications in Table I.

In contrast, **Fig. 2b** illustrates operation with a third-harmonic injection amplitude of  $0.4 \times \hat{U}_{\rm ac}$ . Here, the LF module input power is  $\bar{p}_{\rm x}(t) \neq p_{\rm g,x}(t)$  and the power pulsation is shifted to higher frequencies such that  $\Delta E_{\rm dc} = 4.5\,\rm J$  is reduced by 30% compared to conventional modulation. This was verified experimentally in [17] and a reduction by up to 38% was achieved for a third-harmonic injection amplitude  $0.6 \times \hat{U}_{\rm ac}$  which, however, requires a third-harmonic voltage phase shift  $\phi_{\rm 3rd} = 11^{\circ}$  to maintain grid current controllability.

The concept of CM voltage injection modulation is, however, not limited to third-harmonic voltages and the goal of the subsequent analysis is to identify the optimal LF CM voltage waveform  $\bar{u}_{\rm CM}$  minimizing the dc-link energy buffering requirement  $\Delta E_{\rm dc}$ .

## B. Optimal CM Voltage Waveform Identification

The system in **Fig. 1a** comprises three boost-type PFC rectifier front-ends such that the LF switch node voltage  $\bar{u}_{\bar{\mathbf{x}}\bar{\mathbf{N}}}$  of each module  $x \in \{a,b,c\}$  is limited by the respective dc-link voltage  $U_{\mathrm{dc.x}}$  to values

$$\bar{u}_{\bar{\mathbf{x}}\bar{\mathbf{N}}}(t) = u_{\mathbf{x}}(t) + \bar{u}_{\mathbf{CM}}(t) \in [-U_{dc,\mathbf{x}}(t), U_{dc,\mathbf{x}}(t)].$$

(6)

Hence, for a grid with  $U_{\rm ac}=230\,{\rm V_{rms}}$  (line-to-neutral,  $400\,{\rm V_{rms}}$  line-to-line), a typical dc-link voltage level  $\bar{U}_{\rm dc}=400\,{\rm V}$  is considered here (for completeness, **Appendix A** further provides the optimal CM voltage waveforms for different values of  $\bar{U}_{\rm dc}$  and **Appendix. B** discusses operation in an unbalanced grid) which advantageously allows the use of  $600\,{\rm V}$  power semiconductors and ensures sufficient voltage margin to maintain grid current controllability in case of, e.g., a load step.

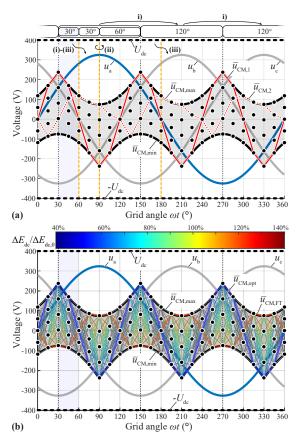

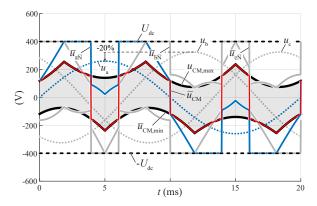

Fig. 3. Discrete LF CM voltage waveform optimization: grid voltages  $u_{\rm a}, u_{\rm b}, u_{\rm c}$ , ideally constant dc-link voltage  $U_{\rm dc} = U_{\rm dc}$ and eligible LF CM voltage range (highlighted by a light gray area) limited by  $\bar{u}_{\rm CM,max}$  and  $\bar{u}_{\rm CM,min}$  according to (7). The considered time- and value-discretized CM voltage values ( $n_u = 5$  and  $n_{\rm t}=25$ ) are highlighted with scatter points: (a) illustration of the symmetry conditions (i)-(iii) and two exemplary CM voltage waveforms  $\bar{u}_{\rm CM,1}$  (complying with the conditions (i)-(iii)) and  $\bar{u}_{\rm CM,2}$ (complying with the condition (i) but violating the conditions (ii) and (iii)). (b) illustration of the n=3125 CM voltage waveforms obtained with (i) and (ii) represented by thin gray lines. The n=25waveforms according to (i)-(iii) are further highlighted with the line color indicating the resulting energy buffering requirement  $\Delta E_{\rm dc}$ relative to  $\Delta E_{\mathrm{dc},0}$  for modulation without CM voltage injection and  $\bar{u}_{\rm CM}=0$ . The best  $\bar{u}_{\rm CM,opt}$  and worst  $\bar{u}_{\rm CM,FT}$  CM voltage waveforms with respect to the resulting  $\Delta E_{\rm dc}$  are highlighted with thicker lines and discussed in more detail in **Fig. 4**.

In the following, the LF fluctuation of the dc-link voltages caused by the LF input power pulsation is neglected, i.e.,  $C_{\rm dc}\gg 100\,\mu{\rm F}$  is assumed such that  $U_{\rm dc,x}(t)=\bar{U}_{\rm dc}$ . Hence, the boost-type converter input voltage limit (6) for all three modules can be solved for the eligible range of the LF CM voltage  $\bar{u}_{\rm CM}$  which is defined by

$$\bar{u}_{\text{CM,max}}(t) = \bar{U}_{\text{dc}} - \max(u_{\text{a}}(t), u_{\text{b}}(t), u_{\text{c}}(t))$$

$$\bar{u}_{\text{CM,min}}(t) = -\bar{U}_{\text{dc}} - \min(u_{\text{a}}(t), u_{\text{b}}(t), u_{\text{c}}(t)), \quad (7)$$

as highlighted in **Fig. 3** for  $\bar{U}_{\rm dc}=400\,{\rm V}$ . Note that current controllability according to (6) is lost in the phase with the instantaneously highest absolute grid voltage value  $|u_{\rm x}|$  in case of  $\bar{u}_{\rm CM}$  exceeding this limit (7).

In order to identify the optimal LF CM voltage waveform  $\bar{u}_{\rm CM}$ , the CM voltage range defined by (7) within one grid period  $T_{\rm ac}=1/f_{\rm ac}$  is discretized with  $n_{\rm t}$  values in the time domain and with  $n_{\rm u}$  CM voltage values.

Fig. 3 illustrates the discretized voltage and time values

with scatter points for  $n_{\rm u}=5$  and  $n_{\rm t}=25$ . The number of possible LF CM voltage waveforms (i.e., the number of permutations for  $n_{\rm u}$  discrete CM voltage values and  $n_{\rm t}$  time positions) grows exponentially with the discretization resolution as  $n=n_{\rm u}^{n_{\rm t}}$  with  $n\approx 3\times 10^{17}$  for the considered example, i.e., an excessive number of paths to be evaluated results even for the low example resolution. However, symmetry considerations allow to drastically decrease the number of paths n:

- (i) The CM voltage waveform must equally impact the energy buffering requirement in all three PFC rectifier front-ends, which corresponds to a  $120^\circ$  symmetry of the CM voltage. Hence, the CM waveforms are only explored within one  $120^\circ$  interval ( $\omega t \in [30^\circ, 150^\circ]$  highlighted in **Fig. 3**). The full 360° waveforms are then obtained by replicating the  $120^\circ$  waveforms (i.e., with  $\bar{u}_{\rm CM}(\omega t) = \bar{u}_{\rm CM}(\omega t + 120^\circ)$ ) and the total number of paths is reduced to  $n = n_{\rm u}^{(n_{\rm t}-1)/3+1} \approx 2 \times 10^6$  for the considered example.

- (ii) Within the considered 120° interval ( $\omega t \in [30^\circ, 150^\circ]$ ), symmetry along the  $\omega t = 90^\circ$  axis is required as otherwise the energy buffering requirement  $\Delta E_{\rm dc}$  is, e.g., decreased in the first 60° segment but increased in the second 60° segment (or vice versa). Hence, the CM voltage waveforms are only explored within the first 60° segment ( $\omega t \in [30^\circ, 90^\circ]$ ) and mirrored to the second segment (i.e.,  $\bar{u}_{\rm CM}(90^\circ + \omega t) = \bar{u}_{\rm CM}(90^\circ \omega t)$ ). With (i) and (ii) the number of paths is reduced to  $n = n_{\rm u}^{(n_{\rm t}-1)/6+1} \approx 3 \times 10^3$  for the considered example.

- (iii) The number of CM waveforms to be evaluated can be further decreased by only considering the waveforms with half-wave symmetry (i.e.,  $\bar{u}_{\rm CM}(180^\circ + \omega t) = -\bar{u}_{\rm CM}(180^\circ \omega t)$ ), as otherwise the energy buffering requirement  $\Delta E_{\rm dc}$  is, e.g., decreased in the first 180° half-period but increased in the second 180° half-period (or vice versa). Combined with (i) and (ii) this results to  $\bar{u}_{\rm CM}(60^\circ + \omega t) = -\bar{u}_{\rm CM}(60^\circ \omega t)$  and  $\bar{u}_{\rm CM}(\omega t = 60^\circ) = 0$  (any signal comprising only triplen harmonics with  $\sin(k \cdot 3f_{\rm ac})$  at multiples  $k \in \mathbb{N}$  of  $3f_{\rm ac}$  results to zero at  $\omega t = 60^\circ$ ) Hence, the valid CM voltage waveforms can be defined upon a single  $30^\circ$  interval and the number of paths is reduced to  $n = n_{\rm u}^{(n_{\rm t}-1)/12} = 25$  for the considered example.

The CM voltage waveforms (calculated in MATLAB) obtained with (i) and (ii) are highlighted in **Fig. 3b** with thin gray lines, and the resulting n=25 valid waveforms according to (i)-(iii) are further highlighted with the line color indicating the resulting energy buffering requirement  $\Delta E_{\rm dc}$  relative to  $\Delta E_{\rm dc,0}$  (modulation without CM injection and  $\bar{u}_{\rm CM}=0$ ). The best  $\bar{u}_{\rm CM,opt}$  and worst  $\bar{u}_{\rm CM,FT}$  CM voltage waveforms with respect to the resulting  $\Delta E_{\rm dc}$  are highlighted with thicker lines in **Fig. 3b** and discussed in more detail in the following.

# C. Optimal CM Voltage Waveform Results

A high-resolution waveform sweep with  $n_{\rm u}=9$  and  $n_{\rm t}=97$  is conducted and the symmetry conditions (i)-(iii) reduce

Fig. 4. Main PFC rectifier front-end waveforms (with focus on phase a) according to the system specifications in Table I and  $C_{\rm dc} \to \infty$  for (a) the optimal (with  $\bar{u}_{\rm CM} = \bar{u}_{\rm CM,opt}, \Delta E_{\rm dc} = 3.6~\rm J)$  and (b) the worst CM voltage waveform (with  $\bar{u}_{\rm CM} = \bar{u}_{\rm CM,FT}, \Delta E_{\rm dc} = 9.0~\rm J)$ : (x.i) sinusoidal grid voltages  $u_{\rm a}, u_{\rm b}, u_{\rm c}$ , LF PFC rectifier front-end input voltages  $\bar{u}_{\rm a\bar{N}}, \bar{u}_{\bar{\rm b}\bar{\rm N}}, \bar{u}_{\bar{\rm c}\bar{\rm N}}$  with respect to the common starpoint N, and ideally constant dc-link voltage  $U_{\rm dc} = \bar{U}_{\rm dc}$ . (x.ii) phase a LF PFC rectifier front-end input voltage  $\bar{u}_{\bar{\rm a}\bar{\rm N}}$ , grid current  $i_{\rm a}$ , and LF input power  $\bar{p}_{\rm a}$  (for comparison the input power  $\bar{p}_{\rm a,0}$  for conventional operation from Fig. 2a is presented with a dotted line).

the number of investigated waveforms from  $n\approx 4\times 10^{92}$  to  $n\approx 43\times 10^6$  which is manageable with state-of-the art compute servers.

The resulting optimal LF CM voltage waveform  $\bar{u}_{\rm CM,opt}$  is very similar to **Fig. 3b** and converges (with increasing resolution  $n_{\rm u}$  and  $n_{\rm t}$ ) to the Discontinuous Pulse Width Modulation (DPWM) strategy (which should not be confused with Digital PWM) highlighted in **Fig. 4a**, where the switch-node  $\bar{x}$  of the phase  $x \in \{a,b,c\}$  with the instantaneous middle absolute grid voltage value  $|u_{\rm x}(t)| = {\rm median}(|u_{\rm a}(t)|, |u_{\rm b}(t)|, |u_{\rm c}(t)|)$  is clamped depending on the instantaneous grid voltage polarity to the positive (if  $u_{\rm x}>0$ ) or negative (if  $u_{\rm x}<0$ ) dc-link rail, and  $\bar{u}_{\rm CM,opt}$  is defined as

$$\bar{u}_{\text{CM,opt}}(t) = \begin{cases} \bar{U}_{\text{dc}} - u_{x}(t), & u_{x}(t) \ge 0\\ -\bar{U}_{\text{dc}} - u_{x}(t), & u_{x}(t) < 0, \end{cases}$$

(8)

which, e.g., for the first 120° interval of the grid period results to

$$\bar{u}_{\rm CM,opt}(t) = \begin{cases} \bar{U}_{\rm dc} - u_{\rm c}(t), & 0^{\circ} < \omega_{\rm ac}t \le 30^{\circ} \\ \bar{U}_{\rm dc} - u_{\rm a}(t), & 30^{\circ} < \omega_{\rm ac}t \le 60^{\circ} \\ -\bar{U}_{\rm dc} - u_{\rm b}(t), & 60^{\circ} < \omega_{\rm ac}t \le 90^{\circ} \\ -\bar{U}_{\rm dc} - u_{\rm c}(t), & 90^{\circ} < \omega_{\rm ac}t \le 120^{\circ}. \end{cases}$$

Such a modulation strategy is known in literature within the context of non-modular/monolithic three-phase PFC acdc converters [21] (featuring a single dc output voltage)

Fig. 5. Main PFC rectifier front-end waveforms (with focus on phase a) according to the system specifications in Table I for optimal CM voltage modulation and (a)  $\bar{U}_{\rm dc}=400\,\rm V$ ,  $C_{\rm dc}=231\,\rm \mu F$  ( $\Delta E_{\rm dc}=3.6\,\rm J$ ,  $\Delta U_{\rm dc}=38.9\,\rm V$ ), (b)  $\bar{U}_{\rm dc}=315\,\rm V$ ,  $C_{\rm dc}=88\,\rm \mu F$  ( $\Delta E_{\rm dc}=4.8\,\rm J$ ,  $\Delta U_{\rm dc}=176.7\,\rm V$ ), (c)  $\bar{U}_{\rm dc}=300\,\rm V$ ,  $C_{\rm dc}=116\,\rm \mu F$  ( $\Delta E_{\rm dc}=4.9\,\rm J$ ,  $\Delta U_{\rm dc}=143.9\,\rm V$ ), and (d)  $\bar{U}_{\rm dc}=290\,\rm V$ ,  $C_{\rm dc}=179\,\rm \mu F$  ( $\Delta E_{\rm dc}=4.9\,\rm J$ ,  $\Delta U_{\rm dc}=95.4\,\rm V$ ): (x.i) sinusoidal grid voltages  $u_{\rm a},u_{\rm b},u_{\rm c}$ , LF PFC rectifier front-end input voltages  $\bar{u}_{\rm a\bar{N}},\bar{u}_{\rm b\bar{N}},\bar{u}_{\rm e\bar{N}}$  with respect to the common starpoint  $\bar{N}$ , and module a dc-link voltage  $U_{\rm dc,a}$  (the average value  $\bar{U}_{\rm dc}$  is represented by a dashed line). (x.ii) phase a LF PFC rectifier front-end input voltage  $\bar{u}_{\bar{a}\bar{N}}$ , grid current  $i_{\rm a}$ , and LF input power  $\bar{p}_{\rm a}$ . (x.iii) module dc-link voltages  $U_{\rm dc,a},U_{\rm dc,b},U_{\rm dc,c}$ , and the resulting minimum  $U_{\rm dc,min}$ , average  $\bar{U}_{\rm dc}$  and maximum  $U_{\rm dc,max}$  values of the dc-link voltages (note that in (a) and (b)  $U_{\rm dc,max}$  equals the maximum blocking voltage of the power semiconductors  $U_{\rm b,max}$ ).

and cascaded modular H-bridge converters [20], and the CM voltage  $\bar{u}_{\rm CM,opt}$  increases the LF module input power  $\bar{p}_{\rm a}$  in the vicinity of  $\omega t=30^{\circ}$  and decreases  $\bar{p}_{\rm a}$  around  $\omega t=90^{\circ}$  compared to  $\bar{p}_{\rm a,0}$  representing the LF input power for conventional operation as comparison.

For this CM voltage waveform  $\bar{u}_{\rm CM,opt}$  the energy buffering requirement of the PFC rectifier front-ends (visualized by the light-gray areas in **Fig. 4a**) results to  $\Delta E_{\rm dc}=3.6\,\rm J$ , i.e., a reduction of 43% is achieved compared to the conventional modulation with  $\bar{u}_{\rm CM}=0$  presented in **Fig. 2a**. Additionally, the semiconductor switching losses are advantageously reduced due to the 1/3 lower number of switching actions (enabled by the DPWM operation where always one out of three PFC rectifier front-ends is in a clamped state) compared to  $\bar{u}_{\rm CM}=0$  (where all PFC rectifier front-ends are continuously switching). Note that the time discretization  $n_{\rm t}$  limits the derivative  ${\rm d}\bar{u}_{\rm CM}/{\rm d}t$  at the CM voltage zero crossing at  $k\cdot 60^{\circ}$  ( $k\in\mathbb{N}$ , see **Fig. 3b**). However, for  $n_{\rm t}=97$  the resulting  $\Delta E_{\rm dc}$  differs by only <1% from the ideal waveforms depicted in **Fig. 4a**.

For completeness, also the worst (with respect to minimizing  $\Delta E_{\rm dc}$ ) CM voltage waveform  $\bar{u}_{\rm CM,FT}$  given by the Flat Top (FT) DPWM [21]-[23] strategy is highlighted in **Fig. 4b.** There, the switch-node  $\bar{x}$  of the phase x with the instantaneous maximum absolute grid voltage value is clamped depending on the instantaneous grid voltage polarity to the positive (if  $u_x > 0$ ) or negative (if  $u_x < 0$ ) dc-link rail. Such a modulation is optimal with respect to switching losses, as the PFC rectifier front-end with the highest instantaneous current values ceases switching and is hence of interest in non-modular/monolithic PFC ac-dc converters without LF energy storage requirement. However, here, the energy buffering requirement of the PFC rectifier front-end increases by 41 % compared to conventional modulation to  $\Delta E_{\rm dc} = 9.0 \, \rm J$ . The reason for this increase in  $\Delta E_{\rm dc}$  becomes obvious from **Fig. 4a.ii** as, e.g., for phase a, the waveform  $\bar{u}_{\mathrm{CM,FT}}$  further increases the module input power  $\bar{p}_{\rm a}$  in the vicinity of  $\omega t = 90^{\circ}$  where the maximum pulsation of the grid power  $p_{g,a}$  occurs.

## D. Minimum DC-Link Voltage / Capacitance Operation

For finite dc-link capacitance values  $C_{

m dc}$  the dc-link voltages fluctuate due to the pulsating LF module input power  $\bar{p}_{x}$ . Given that (6) is fulfilled for all modules throughout the fundamental grid period (i.e., grid current controllability is maintained), the dc-link voltage fluctuation does not impact the generation of the LF CM voltage for, e.g., conventional modulation and third-harmonic voltage injection. This, however, does not apply for the DPWM strategies depicted in **Fig. 4:** If one phase x clamps its switch node  $\bar{x}$  to the corresponding positive dc-link rail, the CM voltage reference for the two remaining PFC rectifier front-ends switching at HF is defined as  $\bar{u}_{\rm CM}(t) = U_{\rm dc,x}(t) - u_{\rm x}(t)$ , i.e., is affected by the LF dc-link voltage fluctuation of phase x. Hence, according to (2) the LF fluctuation of the dc-link voltage  $U_{\rm dc,x}(t)$  impacts the module input power  $\bar{p}_{\rm x}(t)$ , and vice versa, such that no simple analytic expression exists to describe the input voltage, current and power waveforms of the PFC rectifier front-end for finite values of  $C_{\rm dc}$ . Therefore, the numerical calculation of the steady-state input power waveform and the corresponding fluctuation of the dc-link voltages is performed iteratively in MATLAB until the waveforms converge.

Fig. 5a presents the calculated main PFC rectifier front-end waveforms for an average dc-link voltage  $\bar{U}_{\rm dc}=400\,{\rm V}$  and  $C_{\rm dc}=231\,{\rm \mu F}$  in each phase. There, the peak-to-peak dc-link voltage fluctuation results to  $\Delta U_{\rm dc}=38.9\,{\rm V}$  and slightly impacts the generated CM voltage waveform  $\bar{u}_{\rm CM}$ . However, the LF module input power  $\bar{p}_{\rm a}$  is largely identical to Fig. 4a with  $C_{\rm dc}\to\infty$  such that also the resulting  $\Delta E_{\rm dc}=3.6\,{\rm J}$  remains unaffected by the finite dc-link capacitor value.

The relevant question for the practical realization of the optimal CM modulation of Sec. II-C is hence what minimum amount of dc-link capacitance  $C_{\rm dc,min}$  is required in each phase module to assure the safe PFC rectifier front-end operation. For this, two relevant conditions exist: First, the current controllability according to (6) needs to be maintained. Second, the maximum blocking voltage of the power semiconductors must be respected, corresponding in each phase x to the constraint

$$U_{\rm dc,x}(t) \le U_{\rm b,max},$$

(10)

with typically  $U_{\rm b,max}=420\,{\rm V}$  for 600 V power semiconductors to assure a blocking voltage margin of 30 % which is considered in the following.

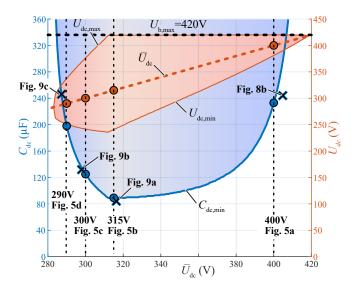

Fig. 6 investigates the minimally required dc-link capacitor value  $C_{\rm dc,min}$  of the optimal CM voltage injection modulation for nominal power operation according to Table I as a function of the average dc-link voltage levels  $\bar{U}_{\rm dc}$ . The steady-state input power waveform and the corresponding fluctuation of the dc-link voltages are again calculated numerically in MATLAB and for a given value of  $\bar{U}_{\rm dc}$ ,  $C_{\rm dc,min}$  is obtained by decreasing  $C_{\rm dc}$  iteratively up to the point where either (6) or (10) is no longer fulfilled.

The previously discussed operating condition in **Fig. 5a** is highlighted in **Fig. 6** and the selected capacitance value corresponds to  $C_{\rm dc,min}=231\,\mu{\rm F}$  for  $\bar{U}_{\rm dc}=400\,{\rm V}$ , which is substantially below  $C_{\rm dc,min,0}=400\,\mu{\rm F}$  required to

Fig. 6. Impact of the average dc-link voltage level  $\bar{U}_{\rm dc}$  on the minimally required dc-link capacitor value  $C_{\rm dc,min}$  for the optimum CM voltage injection modulation of Sec. II-C. The resulting minimum  $U_{\rm dc,min}$ , average  $\bar{U}_{\rm dc}$  and maximum  $U_{\rm dc,max}$  values of the dc-link voltage  $U_{\rm dc,x}(t)$  for nominal power operation according to Table I are highlighted on the second y-axis. Note that  $C_{\rm dc,min}$  is defined by the maximum blocking voltage of the power semiconductors  $U_{\rm b,max}$  for  $\bar{U}_{\rm dc} \geq 315\,{\rm V}$  with  $U_{\rm dc,max} = U_{\rm b,max}$ . The values of  $\bar{U}_{\rm dc}$  and  $C_{\rm dc,min}$  considered in the simulations (Fig. 5) and in the experimental verification (Fig. 9, Fig. 10) are highlighted with a circle and a cross, respectively.

comply with (10) for the conventional operation illustrated in Fig. 2a [14,24]. The resulting minimum values  $U_{\rm dc,min}$  and maximum values  $U_{\rm dc,max}$  within a fundamental period of the dc-link voltage  $U_{\rm dc,x}(t)$  are also highlighted in Fig. 6 on the second y-axis. There it becomes obvious that for  $\bar{U}_{\rm dc}=400\,\rm V$  the minimum dc-link capacitor value  $C_{\rm dc,min}$  is constrained by the maximum dc-link voltage value  $U_{\rm dc,max}$  and (10).

Hence, lowering the average dc-link voltage to  $\bar{U}_{\rm dc} =$  $315\,\mathrm{V}$  (at this point  $C_{\mathrm{dc,min}}$  is equally constrained from (6) and (10)) allows operation with a substantially lower  $C_{\rm dc,min} = 88 \,\mu \rm F$  (i.e., a 62% reduction compared to  $\bar{U}_{\mathrm{dc}} = 400\,\mathrm{V}$ ). Note that now the grid voltage amplitude is larger than the average dc-link voltage  $\hat{U}_{\mathrm{ac}} > \bar{U}_{\mathrm{dc}}$  (i.e., conventional operation with  $\bar{u}_{\rm CM}=0$  is not possible) and the corresponding main PFC rectifier front-end waveforms are presented in Fig. 5b. Here, the dc-link capacitor utilization is high (i.e., a small  $C_{

m dc}$  is sufficient to maintain PFC rectifier operation) and a voltage fluctuation of  $\Delta U_{\rm dc} = 176.7 \, {\rm V}$ results. This heavily impacts the input power waveforms and increases the energy buffering requirement to  $\Delta E_{\rm dc} = 4.8 \, \rm J.$ Note that such a high  $\Delta U_{\rm dc}$  imposes substantial current stresses on the dc-link capacitors  $C_{\rm dc}$  and a wide inputvoltage range for the subsequent isolated dc-dc converter stages which needs to be considered in the system design.

Then, for a further decrease of the average dc-link voltage  $\bar{U}_{\rm dc}$ , the minimum dc-link capacitor value  $C_{\rm dc,min}$  is constrained by (6) and increases again. E.g., for  $\bar{U}_{\rm dc}=300\,{\rm V}$  (Fig. 5c) and  $\bar{U}_{\rm dc}=290\,{\rm V}$  (Fig. 5d), a minimum dc-link capacitor value of  $C_{\rm dc,min}=116\,{\rm \mu F}$  and  $C_{\rm dc,min}=179\,{\rm \mu F}$ , respectively, is required and compared to  $\bar{U}_{\rm dc}=315\,{\rm V}$  the dc-link voltage fluctuation reduces again.

Fig. 7. Considered PFC rectifier control structure comprising the saturable CM voltage modulator from [20,25] setting  $u_{\text{CM,s}}$  such that in each module x the LF switch node voltage  $\bar{u}_{\bar{x}\bar{N}}(t)$  remains below the limit imposed by the dc-link voltage  $U_{\text{dc,x}}(t)$ , i.e.,  $\bar{u}_{\bar{x}\bar{N}}(t) \in [-U_{\text{dc,x}}(t), U_{\text{dc,x}}(t)]$ .

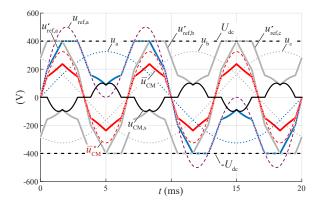

Fig. 8. Simplified voltage waveforms of the PFC rectifier control structure in Fig. 7: A large open-loop third-harmonic voltage reference  $\bar{u}_{\rm CM}^*$  is added to the grid voltages  $u_{\rm a}, u_{\rm b}, u_{\rm c}$  which results in reference voltages  $u_{\rm ref,a}, u_{\rm ref,b}, u_{\rm ref,c}$  (only  $u_{\rm ref,a}$  is shown) exceeding the (ideally constant) dc-link voltage  $U_{\rm dc}$ . To maintain grid current controllability according to (6) the saturable CM voltage modulator [20] adds a correction term  $u_{\rm CM,s}$ , resulting in the final reference voltages  $u'_{\rm ref,a}, u'_{\rm ref,b}, u'_{\rm ref,c}$  with the CM component  $\bar{u}_{\rm CM}$  which is very similar to the optimal CM voltage waveform in Fig. 4a but shows limited  ${\rm d}\bar{u}_{\rm CM}/{\rm d}t$  values at the CM voltage zero crossing at  $k\cdot 60^\circ$  ( $k\in\mathbb{N}$ ).

In closing it can be stated that the optimal CM modulation of **Sec. II-C** enables operation with lower dc-link capacitor values  $C_{\rm dc}$  and/or lower average dc-link voltage  $\bar{U}_{\rm dc}$  compared to conventional operation and the goal is hence to verify these findings in practice.

# III. PFC RECTIFIER CONTROL WITH OPTIMAL CM INJECTION MODULATION

The identified optimum modulation requires a special control structure for the three PFC rectifier front-ends [20]–[23,25] as for a given point in time one out of three phases completely ceases switching and clamps the switch node potential to either the positive or negative dc-link rail and the remaining two phases realize sinusoidal three-phase grid currents  $i_{\rm a}, i_{\rm b}, i_{\rm c}$  resulting in a collaborative control where the burden of the grid current control is shared among the PFC rectifier front-ends.

The considered cascaded PFC rectifier control structure is depicted in **Fig. 7**. The dc-link voltage regulator  $RU_{\rm dc}$  (implemented as a Proportional-Integral (PI) controller) sets a grid conductivity reference value  $G^* = \hat{I}_{\rm ac}^*/\hat{U}_{\rm ac}$  (i.e., the grid current amplitude reference  $\hat{I}_{\rm ac}^*$  normalized by the

grid voltage amplitude  $\hat{U}_{\rm ac}$ , with the unit  $\Omega^{-1}$ ) based on the instantaneous dc-link voltage error and the dc module output current feed-forward term  $I_{\rm dc}$ . Note that here the instantaneous mean dc-link voltage  $\frac{1}{3}\sum_{x\in\{a,b,c\}}U_{\rm dc,x}$  is considered to later obtain symmetric three-phase current references. In case the dc-link voltage balancing among the three-modules cannot be guaranteed by the subsequent isolated dc-dc converter stages, the control strategy of [2,26] would need to be implemented.

A sinusoidal grid current reference value  $i_{\rm x}^*$  with  $x \in \{a,b,c\}$  is then obtained by multiplying  $G^*$  with the respective grid voltage  $u_{\rm x}$ . The grid current reference values are then tracked by the phase current controllers  $Ri_{\rm x}$  (again implemented as PI controllers) where only two out of three grid currents are regulated (here the currents of phase a and b) and the third control signal is derived with a symmetry condition as only two degrees of freedom exist for the grid currents in an open-starpoint configuration of three PFC rectifier front-ends.

Next, the measured grid voltages are added as feedforward terms to the phase current controller outputs. The optimal CM voltage injection is realized by means of the saturable CM voltage modulator from [20] with the main controller voltage waveforms highlighted in Fig. 8: A large open-loop CM voltage reference  $\bar{u}_{\rm CM}^* = M_{\rm 3rd}$  ·  $\hat{U}_{\rm ac} \sin(3\omega_{\rm ac}t)$  (with e.g.,  $M_{\rm 3rd}=1.0$ ) is added as a feedforward term to the controller outputs. It is important to clarify that for  $\bar{U}_{\rm dc} = 400\,\mathrm{V}$  the resulting voltage reference  $u_{\rm ref,x}$  with  $M_{\rm 3rd}=1.0$  violates the current controllability constraint (6). Therefore, in a second step the saturable CM voltage modulator sets a correction term  $u_{\rm CM,s}$  such that in each module x the final reference voltage  $u'_{\rm ref,x}(t)$ remains below the limit imposed by the dc-link voltage  $U_{

m dc,x}(t)$  (corresponding to  $u_{ar{

m x}ar{

m N}} \in [-U_{

m dc,x}(t),U_{

m dc,x}(t)]$ ). Finally, the adjusted reference voltages  $u'_{\rm ref,x}$  are translated into modulation indices  $m_{\rm x} \in [-1,1]$  by division with the respective instantaneous dc-link voltage which allows to generate the power semiconductor control signals in each PFC rectifier front-end by means of PWM for the HF bridgeleg and based on the sign of  $m_{\mathrm{x}}$  for the LF bridge-leg (see Fig. 1a).

Note that by increasing  $M_{3\mathrm{rd}}$ , the  $\mathrm{d}\bar{u}_{\mathrm{CM}}/\mathrm{d}t$  at the CM voltage zero crossing (occurring at  $k\cdot 60^\circ$  ( $k\in\mathbb{N}$ ) becomes increasingly steep and approaches the ideal waveforms of

Fig. 4a where a CM voltage step occurs when the clamping reference transitions from one phase to another. However, as found in Sec. II-C the finite  $\mathrm{d}\bar{u}_{\mathrm{CM}}/\mathrm{d}t$  (resulting there as a consequence of the time discretization) only marginally impacts the energy buffering requirement  $\Delta E_{\mathrm{dc}}$ . Further, a CM voltage reference step might negatively impact the current controllers, such that  $M_{\mathrm{3rd}}=1.0$  is considered in the experimental verification of the concept.

#### IV. EXPERIMENTAL VERIFICATION

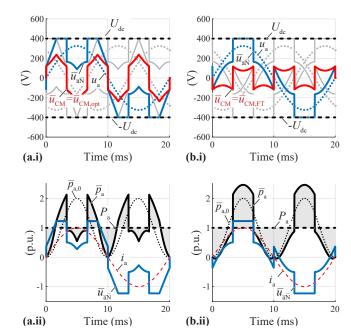

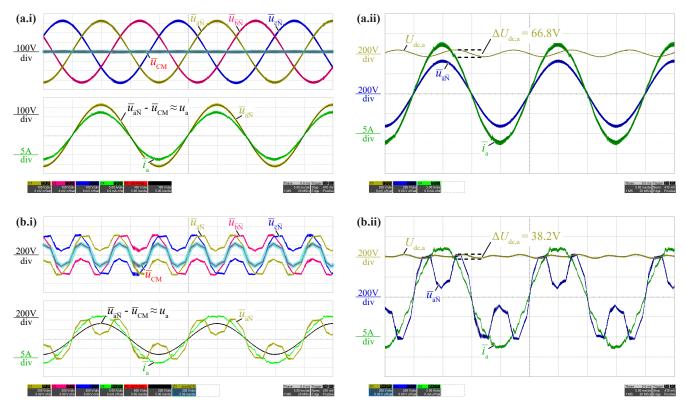

For the experimental verification of the proposed concept an existing  $6\,kW$  prototype system according to Table I is employed and details on the hardware can be found in Ref. [17]. The converter comprises three single-phase PFC rectifier front-ends and three individual resistive loads are used to emulate the subsequent isolated dc-dc converter stages and for the operating point in Fig. 9a the dc-link voltage (and hence module dc output current) fluctuation remains below  $\pm 10\,\%$ .

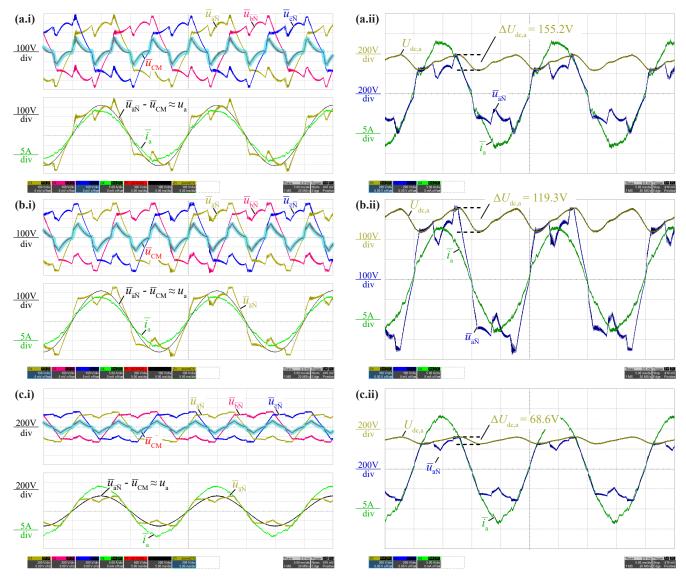

Experimental nominal power PFC rectifier front-end waveforms for conventional modulation with  $\bar{u}_{\rm CM}=0$  are depicted in **Fig. 9a** where a sinusoidal grid current  $i_{\rm a}$  can be observed. **Table II** lists the measured performance with  $\Delta E_{\rm dc}=6.5\,\rm J$  (serving in the following as the base value for the relative energy buffering reduction) buffered by the dclink capacitor in phase a. Note that here, the maximum value of the dc-link voltage  $U_{\rm dc,max}$  exceeds the target value from (10) of  $U_{\rm b,max}=420\,\rm V$  which prevents the use of 600 V power semiconductors (as discussed in **Sec. II-D** a dc-link capacitor minimum value of  $C_{\rm dc,min,0}=400\,\rm \mu F$  is required to allow sufficient voltage blocking margin for  $\bar{u}_{\rm CM}=0$ ). This, however, is not problematic for the prototype system (also allowing operation in delta-configuration with  $\bar{U}_{\rm dc}=700\,\rm V$ ) employing 1.2 kV sic power semiconductors.

**Fig. 9b** depicts the main converter waveforms for the optimal CM voltage modulation from **Sec. II-C**: There, the PFC rectifier front-end voltages are non-sinusoidal and only two out of three modules perform operation with PWM at any given point in time and  $\Delta E_{\rm dc}=3.8\,\rm J$  is reduced – as predicted – by more than 40% compared to **Fig. 9a**. The large CM voltage injection slightly increases the grid current distortion, however, the grid current  $i_{\rm a}$  remains sinusoidal and a small Total Harmonic Distortion (THD) of  $3.0\,\%$  results.

Next, the goal is to verify the operation limits of the optimal CM voltage modulation with respect to minimum average dc-link voltage  $\bar{U}_{\rm dc}$  and/or dc-link capacitance  $C_{\rm dc}$  according to Sec. II-D. The nominal dc-link capacitance of the prototype system is  $C_{\rm dc}=240\,\rm \mu F=6\times40\,\rm \mu F$  realized with film capacitors and can be decreased in steps of  $40\,\rm \mu F$  to approximate the operating conditions highlighted in Fig. 6. The dc-link capacitance  $C_{\rm dc}$  measured with an LCR-meter slightly deviates from the nominal capacitance value due to component tolerances and is stated in Table II for each considered operating point.

**Fig. 10a** presents operation with an average dc-link voltage reduced to  $\bar{U}_{\rm dc}=317\,{\rm V}$  which enables minimum dc-link capacitance operation with  $C_{\rm dc}=80\,{\rm \mu F}$  while complying with (6) and (10). The grid current  $i_{\rm a}$  shows

notable distortion but remains largely sinusoidal despite the massive dc-link voltage fluctuation  $\Delta U_{\rm dc}$  and the grid current THD results to 5.9%. It is important to highlight that  $\Delta E_{\rm dc} = 5.0\,\rm J$  is elevated compared to Fig. 9b. Hence, this operating condition represents the maximum dc-link capacitor utilization, i.e., a small  $C_{\rm dc}$  (with a large voltage fluctuation  $\Delta U_{\rm dc}$ ) is sufficient to maintain PFC rectifier operation, and not the minimum energy buffering requirement. Despite this large dc-link voltage fluctuation  $\Delta U_{\rm dc}$ , the measured buffered energy  $\Delta E_{\rm dc}$  (with resistive loads) closely matches the calculated value (where isolated dc-dc converter stages with constant input power are considered) with a small deviation <5%.

When further lowering the average dc-link voltage  $\bar{U}_{\rm dc}$  the minimally required dc-link capacitor value  $C_{\rm dc}$  increases again and **Fig. 10b** presents converter waveforms for  $\bar{U}_{\rm dc}=298\,{\rm V}$  and  $C_{\rm dc}=120\,{\rm \mu F},$  with  $\Delta E_{\rm dc}=5.1\,{\rm J}.$  There, the dc-link voltage fluctuation  $\Delta U_{\rm dc}$  is reduced compared to **Fig. 10a** such that also the grid current quality is notably improved with a THD of 4.1 %.

Last, **Fig. 10c** presents experimental waveforms close to the lower bound of feasible average dc-link voltage with  $\bar{U}_{\rm dc}=284\,{\rm V}$  where the dc-link capacitor values are increased again to  $C_{\rm dc}=240\,{\rm \mu F}$ . There, the maximum dc-link voltage advantageously remains low with  $U_{\rm dc,max}<320\,{\rm V}$  and  $\Delta E_{\rm dc}=4.9\,{\rm J}$ .

In closing it can be stated that the optimal CM modulation of **Sec. II** and the associated energy buffering savings and extreme operating conditions with minimum dc-link voltage and/or capacitance are successfully verified by the experimental results provided in this section.

#### V. CONCLUSION

The phase-modular isolated three-phase Power Factor Correction (PFC) ac-dc converter structure with individual isolated dc-dc converter stages presented in **Fig. 1a** advantageously facilitates the use of standard single-phase equipment and the low 400 V dc-link voltage level allows to use high performance 600 V semiconductors. The main drawback of this topology, however, is the fact that the time-varying single-phase input power only sums to a constant three-phase output power at the isolated dc output voltage, such that large dc-link capacitor values are required. Therefore, recent literature proposes to reduce the dc-link energy buffering requirement  $\Delta E_{\rm dc}$  by means of a third-harmonic Common-Mode (CM) voltage injection modulation.

This paper identifies the optimal CM voltage waveform with respect to minimizing  $\Delta E_{\rm dc}$  which results in a collaborative modulation where for a given point in time only two out of three phases operate with Pulse Width Modulation (PWM) while the third phase ceases switching. Further, optimal CM voltage modulation with reduced dc-link voltage levels and/or dc-link capacitance values is investigated. Experimental results with a 6 kW prototype system yield a reduction in  $\Delta E_{\rm dc}$  by up to 42 % or, alternatively, operation with an average dc-link voltage below 285 V, which closely match the theoretical considerations.

Fig. 9. Experimental nominal power PFC rectifier front-end waveforms obtained with a 6 kW prototype system according to the system specifications in **Table I** for (a) conventional modulation (with  $\bar{u}_{\rm CM}=0$ ,  $\Delta E_{\rm dc}=6.5\,\rm J$ ) and (b) optimal CM voltage injection (with  $\bar{u}_{\rm CM,opt}$ ,  $\Delta E_{\rm dc}=3.8\,\rm J$ ): (x.i) LF PFC rectifier front-end input voltages  $\bar{u}_{\bar{a}\bar{N}},\bar{u}_{\bar{b}\bar{N}},\bar{u}_{\bar{c}\bar{N}}$ , LF CM voltage  $\bar{u}_{\rm CM}=\frac{1}{3}(\bar{u}_{\bar{a}\bar{N}}+\bar{u}_{\bar{b}\bar{N}}+\bar{u}_{\bar{c}\bar{N}})$  (highlighted with a semi-transparent cyan line), and grid current  $i_a$  of phase a. (x.ii) phase a LF PFC rectifier front-end input voltage  $\bar{u}_{\bar{a}\bar{N}}$ , grid current  $i_a$ , and dc-link voltage  $U_{\rm dc,a}$ .

TABLE II: MEASUREMENT RESULTS.

| Mod.     | $C_{ m dc}$ nom. (meas.) | $U_{ m dc}$ meas. | $U_{ m dc,max}$ meas. | $U_{ m dc,min}$ meas. | $\Delta E_{ m dc}$ meas. (meas. rel.) | $\Delta E_{ m dc}$ calc. | THD <sub>40</sub> meas. |

|----------|--------------------------|-------------------|-----------------------|-----------------------|---------------------------------------|--------------------------|-------------------------|

| Fig. 9a  | 240 μF (244 μF)          | 400 V             | 433 V                 | 367 V                 | 6.5 J (100 %)                         | 6.4 J                    | 1.4 %                   |

| Fig. 9b  | 240 μF (244 μF)          | 405 V             | 425 V                 | 385 V                 | 3.8 J (58.4 %)                        | 3.6 J                    | 3.0 %                   |

| Fig. 10a | 80 μF (84 μF)            | 317 V             | 390 V                 | 235 V                 | 5.0 J (77.0 %)                        | 4.8 J                    | 5.9 %                   |

| Fig. 10b | 120 μF (124 μF)          | 298 V             | 358 V                 | 238 V                 | 5.1 J (79.4 %)                        | 4.9 J                    | 4.1 %                   |

| Fig. 10c | 240 μF (244 μF)          | 284 V             | 319 V                 | 250 V                 | 4.9 J (76.0 %)                        | 4.9 J                    | 3.9 %                   |

#### REFERENCES

- D. Chapman, D. James, and C. J. Tuck, "A high density 48 V 200 A rectifier with power factor correction-an engineering overview," in *Proc. of the IEEE International Telecommunications Energy Conference (INTELEC)*, vol. 1, 1993, pp. 118–125.

R. Greul, S. D. Round, and J. W. Kolar, "Analysis and control of

- [2] R. Greul, S. D. Round, and J. W. Kolar, "Analysis and control of a three-phase, unity power factor Y-rectifier," *IEEE Transactions on Power Electronics*, vol. 22, no. 5, pp. 1900–1911, 2007.

- [3] A. Singh, A. Mallik, and A. Khaligh, "A comparative study of failure-tolerant three-phase RTRUs for more electric aircrafts," in *Proc. of the IEEE Applied Power Electronics Conference and Exposition (APEC)*, 2019, pp. 1121–1127.

- [4] F. Vollmaier, A. Connaughton, T. Langbauer, and K. Krischan, "Exploiting a multi-port transformer for minimal DC-link capacitance for an automotive onboard charger," in *Proc. of the European Conference on Power Electronics and Applications (EPE ECCE Europe)*, 2020, pp. 1–8.

- [5] H. Kim, J. Park, S. Kim, R. M. Hakim, H. P. Kieu, and S. Choi, "Single-stage EV on-board charger with single-and three-phase grid compatibility," in *Proc. of the IEEE Applied Power Electronics Conference and Exposition (APEC)*, 2021, pp. 583–589.

- [6] S. Kampel and R. Garcia, "2500 W full-bridge totem-pole power factor correction using CoolGaNTM," Tech. Rep. AN\_201702\_PL52\_011,

- 2018. [Online]. Available: https://www.infineon.com/cms/en/product/evaluation-boards/eval\_2500w\_pfc\_gan\_a/

- [7] J. W. Kolar and T. Friedli, "The essence of three-phase PFC rectifier systems - Part I," *Transactions on Power Electronics*, vol. 28, no. 1, pp. 176–198, 2013.

- [8] H. Mao, F. C. Lee, D. Boroyevich, and S. Hiti, "High performance three-phase power factor correction circuits," in *Proc. of the IEEE Conference on Industrial Electronics (IECON)*, vol. 1, 1995, pp. 8–14.

- [9] M. Makoschitz, M. Hartmann, and H. Ertl, "Hardware implementation and characterization of SiC-based hybrid three-phase rectifier employing third harmonic injection," in *Proc. of the IEEE Applied Power Electronics Conference and Exposition (APEC)*, 2016, pp. 1–8.

- [10] X. Gong, G. Wang, and M. Bhardwaj, "6.6kW three-phase Interleaved totem pole PFC design with 98.9% peak efficiency for HEV/EV onboard charger," in *Proc. of the IEEE Applied Power Electronics Conference (APEC)*, 2019, pp. 2029–2034.

- [11] J. Azurza Anderson, G. Zulauf, P. Papamanolis, S. Hobi, S. M. Miric, and J. W. Kolar, "Three levels are not enough: Scaling laws for multi-level converters in AC/DC applications," *IEEE Transactions on Power Electronics*, vol. 36, no. 4, pp. 3967–3986, 2020.

- [12] F. Vollmaier, A. Connaughton, I. Recepi, T. Langbauer, M. Pajnic, W. Konrad, and C. Mentin, "Tiny power box Exploiting multiport series resonant topologies for very high power density onboard

Fig. 10. Experimental nominal power PFC rectifier front-end waveforms for optimal CM voltage injection obtained with a 6 kW prototype system according to the system specifications in **Table I** and with minimum average dc-link voltage  $\bar{U}_{\rm dc}$  and/or dc-link capacitor  $C_{\rm dc}$  values (see **Fig. 6**), i.e., (a)  $\bar{U}_{\rm dc}=317\,\rm V$ ,  $C_{\rm dc}=80\,\mu\rm F$ , and  $\Delta E_{\rm dc}=5.0\,\rm J$ , (b)  $\bar{U}_{\rm dc}=298\,\rm V$ ,  $C_{\rm dc}=120\,\mu\rm F$ , and  $\Delta E_{\rm dc}=5.1\,\rm J$ , (c)  $\bar{U}_{\rm dc}=284\,\rm V$ ,  $C_{\rm dc}=240\,\mu\rm F$ , and  $\Delta E_{\rm dc}=4.9\,\rm J$ . (x.i) LF PFC rectifier front-end input voltages  $\bar{u}_{\bar{a}\bar{N}}, \bar{u}_{\bar{b}\bar{N}}, \bar{u}_{\bar{c}\bar{N}}$ , LF CM voltage  $\bar{u}_{\rm CM}=\frac{1}{3}(\bar{u}_{\bar{a}\bar{N}}+\bar{u}_{\bar{c}\bar{N}})$  (highlighted with a semi-transparent cyan line), and grid current  $i_a$  of phase a. (x.ii) phase a LF PFC rectifier front-end input voltage  $\bar{u}_{\bar{a}\bar{N}}$ , grid current  $i_a$ , and dc-link voltage  $U_{\rm dc,a}$ .

- chargers," in Proc. of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management (PCIM Europe), 2022, pp. 1–9.

- [13] Q. Huang and A. Q. Huang, "Review of GaN totem-pole bridgeless PFC," CPSS Transactions on Power Electronics and Applications, vol. 2, no. 3, pp. 187–196, 2017.

- [14] D. Menzi, M. J. Azurza Anderson, Jonand Kasper, and J. W. Kolar, "New third-harmonic injection modulation reducing the DC-link energy buffer requirement of phase-modular three-phase isolated PFC AC / DC converter systems," in Proc. of the IEEE Workshop on Control and Modeling for Power Electronics (COMPEL) 2021

- Control and Modeling for Power Electronics (COMPEL), 2021.

[15] G. Buja and G. Indri, "Improvement of pulse width modulation techniques," Archiv für Elektrotechnik, vol. 57, no. 5, pp. 281–289, 1975

- [16] H. van der Broeck, H.-C. Skudelny, and G. Stanke, "Analysis and realization of a pulsewidth modulator based on voltage space vectors," *IEEE Transactions on Industry Applications*, vol. 24, no. 1, pp. 142– 150, 1988.

- [17] T. Langbauer, D. Menzi, V. Marugg, F. Vollmaier, J. Azurza, M. Kasper, and J. W. Kolar, "Third-harmonic-type modulation minimizing the DC-link energy storage requirement of isolated phasemodular three-phase PFC rectifier systems," *IEEE Access*, vol. 11, pp. 34359–34371, 2023.

- pp. 34 359–34 371, 2023.

Z. Li, R. Lizana, A. V. Peterchev, and S. M. Goetz, "Ripple current

- suppression methods for star-configured modular multilevel converters," in *Proc. of the Annual Conference of the IEEE Industrial Electronics Society (IECON)*, 2017, pp. 1505–1510.

- [19] Z. Li, R. Lizana, Z. Yu, S. Sha, A. V. Peterchev, and S. M. Goetz, "Modulation and Control of Series/Parallel Module for Ripple-Current Reduction in Star-Configured Split-Battery Applications," *IEEE Transactions on Power Electronics*, vol. 35, no. 12, pp. 12977–12987, 2020.

- [20] R. Unruh, F. Schafmeister, and J. Böcker, "Zero-sequence voltage reduces DC-link capacitor demand in cascaded H-bridge converters for large-scale electrolyzers by 40%," in *Proc. of the IEEE European Conference on Power Electronics and Applications (EPE - ECCE Europe)*, 2022, pp. 1–10.

- [21] J. W. Kolar, H. Ertl, and F. Zach, "Influence of the modulation method on the conduction and switching losses of a PWM converter system," *IEEE Transactions on Industry Applications*, vol. 27, no. 6, pp. 1063 – 1075, 1991.

- [22] M. Depenbrock, "Pulse width control of a 3-phase inverter with nonsinusoidal phase voltages," in *Proc. of the IEEE/IAS International* Semiconductor Power Converter Conference, 1977, pp. 399–403.

- [23] A. M. Hava, R. J. Kerkman, and T. A. Lipo, "A high-performance generalized discontinuous PWM algorithm," *IEEE Transactions on Industry Applications*, vol. 34, no. 5, pp. 1059–1071, 1998.

- [24] A. Marcos-Pastor, E. Vidal-Idiarte, A. Cid-Pastor, and L. Martínez-Salamero, "Minimum DC-link capacitance for single-phase applications with power factor correction," *IEEE Transactions on Industrial Electronics*, vol. 67, no. 6, pp. 5204–5208, 2020.

- [25] R. Unruh, J. Lange, F. Schafmeister, and J. Böcker, "Adaptive zero-sequence voltage injection for modular solid-state transformer to compensate for asymmetrical fault conditions," in *Proc. of the IEEE European Conference on Power Electronics and Applications (EPE ECCE Europe)*, 2021, pp. 1–10.

- [26] P. Cortes, J. Huber, M. Silva, and J. W. Kolar, "New modulation and control scheme for phase-modular isolated matrix-type three-phase AC/DC converter," in *Proc. of the Annual Conference of the IEEE Industrial Electronics Society (IECON)*, 2013, pp. 4899–4906.

#### APPENDIX A

# IMPACT OF THE DC-LINK VOLTAGE ON THE OPTIMAL CM VOLTAGE TRAJECTORY

The analysis in **Sec. II** is limited to  $\bar{U}_{\rm dc}=400\,\mathrm{V}$  and this Appendix further provides the optimal CM voltage trajectories obtained with the method from **Sec. II-B** for different dc-link voltage levels  $\bar{U}_{\rm dc}=\{300\,\mathrm{V},400\,\mathrm{V},500\,\mathrm{V},600\,\mathrm{V}\}.$

Fig. 11a considers  $\bar{U}_{\rm dc}=300\,{\rm V}$  with  $\bar{U}_{\rm dc}<\hat{U}_{\rm ac}$  such that the eligible LF CM voltage range according (7) does not allow for conventional modulation with  $\bar{u}_{\rm CM}=0$  as  $\bar{u}_{\rm CM,max}$  and  $\bar{u}_{\rm CM,min}$  change signs during one fundamental period. Here, the optimal CM voltage trajectory  $\bar{u}_{\rm CM,opt}$  results in  $\Delta E_{\rm dc}=4.6\,{\rm J}$  and corresponds to a DPWM strategy, where the switchnode  $\bar{x}$  of the phase x with the instantaneous middle absolute grid voltage value is clamped to the positive (if  $u_{\rm x}>0$ ) or negative (if  $u_{\rm x}<0$ ) dc-link rail [20,21]. Hence, the same modulation strategy is optimal for both  $\bar{U}_{\rm dc}=300\,{\rm V}$  and  $\bar{U}_{\rm dc}=400\,{\rm V}$  (shown in Fig. 11b for completeness) where

the larger range of eligible CM voltages (7) with  $\bar{U}_{\rm dc} = 400\,\mathrm{V}$  enables an improved energy buffering requirement of  $\Delta E_{\rm dc} = 3.6\,\mathrm{J}$  compared to  $\bar{U}_{\rm dc} = 300\,\mathrm{V}$  with  $\Delta E_{\rm dc} = 4.6\,\mathrm{J}$

For a further increase in the dc-link voltage (**Fig. 11c,d**), the optimal CM voltage injection strategy changes, as the continuous clamping of the middle phase would overcompensate the instantaneous power pulsation, and  $\Delta E_{\rm dc}=3.1\,\rm J$  and  $\Delta E_{\rm dc}=3.0\,\rm J$  can be achieved for  $\bar{U}_{\rm dc}=500\,\rm V$  and  $\bar{U}_{\rm dc}=600\,\rm V$ , respectively, which is below the theoretically achievable limit for pure third-harmonic voltage injection modulation [14]. However, it is important to highlight that for  $\bar{U}_{\rm dc}=500\,\rm V$  and  $\bar{U}_{\rm dc}=600\,\rm V$  power semiconductors with a rated voltage  $>600\,\rm V$  are required, thereby mitigating one of the main advantages of the converter concept such that these dc-link voltage levels are less of a practical interest.

# APPENDIX B OPERATION IN UNBALANCED MAINS

The analysis in **Sec. II** is performed assuming an ideally symmetric three-phase grid. In case of a grid voltage imbalance the range of feasible LF CM voltages (7) (to satisfy the boost-type ac-dc converter voltage limit according to (6)) is altered and **Fig. 12** presents the resulting maximum  $\bar{u}_{\rm CM,max}$  and minimum CM voltage  $\bar{u}_{\rm CM,min}$  for a 20% reduced voltage amplitude  $\hat{U}_{\rm ac}$  in phase a. Despite the grid voltage imbalance, the clamping strategy from II-C can be employed, where the resulting LF CM voltage waveform  $\bar{u}_{\rm CM}$  is no longer 120° symmetric.

Fig. 11. Optimal LF CM voltage waveform (evaluated with  $n_{\rm u}=9$  and  $n_{\rm t}=73$ ) for the system specifications in Table I, with  $C_{\rm dc}\to\infty$ , and (a)  $\bar{U}_{\rm dc}=300\,{\rm V}$  ( $\Delta E_{\rm dc}=4.6\,{\rm J}$ ), (b)  $\bar{U}_{\rm dc}=400\,{\rm V}$  ( $\Delta E_{\rm dc}=3.6\,{\rm J}$ ), (c)  $\bar{U}_{\rm dc}=500\,{\rm V}$  ( $\Delta E_{\rm dc}=3.1\,{\rm J}$ ), (d)  $\bar{U}_{\rm dc}=600\,{\rm V}$  ( $\Delta E_{\rm dc}=3.0\,{\rm J}$ ): (x.i) grid voltages  $u_{\rm a},u_{\rm b},u_{\rm c}$ , ideally constant dc-link voltage  $U_{\rm dc}=\bar{U}_{\rm dc}$ , eligible LF CM voltage range (highlighted by a light gray area) limited by  $\bar{u}_{\rm CM,max}$  and  $\bar{u}_{\rm CM,min}$  according to (7), and optimal CM voltage waveform  $\bar{u}_{\rm CM,opt}$ . (x.ii) phase a LF PFC rectifier front-end input voltage  $\bar{u}_{\bar{a}\bar{N}}$ , grid current  $i_{\rm a}$ , and LF input power  $\bar{p}_{\rm a}$ .

**Fig. 12.** Optimal LF CM voltage waveform from **Fig. 4a** for an unbalanced grid where the phase a voltage amplitude  $\hat{U}_{\rm ac}$  is decreased by 20 %: grid voltages  $u_{\rm a}, u_{\rm b}, u_{\rm c}$ , ideally constant dclink voltage  $U_{\rm dc} = \bar{U}_{\rm dc}$ , LF PFC rectifier front-end input voltages  $\bar{u}_{\bar{\rm a}\bar{\rm N}}, \bar{u}_{\bar{\rm b}\bar{\rm N}}, \bar{u}_{\bar{\rm c}\bar{\rm N}}$ , eligible LF CM voltage range (highlighted by a light gray area) limited by  $\bar{u}_{\rm CM,max}$  and  $\bar{u}_{\rm CM,min}$  according to (7), and optimal CM voltage waveform  $\bar{u}_{\rm CM}$ .

Fig. 13. Phase-modular three-phase isolated PFC ac-dc converter system with a delta  $(\Delta)$  arrangement of the PFC rectifier front-ends [17] (with a typical average dc-link voltage level of  $\bar{U}_{\rm dc}=700\,\rm V$  for a grid with  $230\,\rm V_{rms}$  line-to-neutral voltage): The LF CM current circulating inside the  $\Delta$ -connection (the current path is highlighted with a red dashed line) does not impact the grid currents and allows to alter the LF input power flows of the modules.

#### APPENDIX C

## OPTIMAL CM CURRENT INJECTION MODULATION OF DELTA-CONNECTED PHASE-MODULAR ISOLATED THREE-PHASE PFC AC-DC CONVERTERS

It is important to highlight that the discussed optimal CM modulation strategy can also be employed to a delta ( $\Delta$ ) arrangement of the PFC rectifier front-ends [17] where an LF CM  $current~\bar{i}_{\rm CM}$  circulates between the modules (the CM current path is highlighted in **Fig. 13**) and thereby allows to redistribute the grid input power pulsation. Here, the three module input currents  $i_{\bar{a}}, i_{\bar{b}}, i_{\bar{c}}$  are individually controlled and details on the required control structure can be found

in [17]. Further, the dc-link voltages do not directly impose an upper bound for the LF CM current reference (as it is the case for the LF CM voltage reference with (7) for the star-connection of the modules in **Fig. 1a**). However, high values of the LF CM current amplitude are accompanied by additional conduction losses in the ac-dc front-end power semiconductors and boost inductors L (which are then also required to feature a higher saturation compared to conventional modulation with  $\bar{i}_{\rm CM}=0$ ), such that the optimal LF CM current waveform  $\bar{i}_{\rm CM,opt}$  cannot be identified a priori for a given grid voltage amplitude and dc-link voltage level (as it is the case for the star-connection of the modules in **Fig. 1a**), but needs to be assessed separately for each specific converter design.

David Menzi (M'22) received his B.Sc. and M.Sc. degree in Electrical Engineering and Information Technology at the Swiss Federal Institute of Technology (ETH), Zurich, Switzerland, in 2015 and 2017, respectively, and also spent a semester at the Royal Institute of Technology (KTH) in Stockholm, Sweden as an exchange student. During his studies, he worked at ABB Medium Voltage Drives (MVD) in Turgi, Switzerland, as an intern and working student. He conducted his Ph.D. research in Electrical Engineering from 2018 to

2022 on bidirectional phase-modular three-phase buck-boost converter systems under the supervision of Prof. J.W. Kolar at the Power Electronic Systems Laboratory (PES) of ETH Zurich, and was awarded the EPCIA Student Award 2022 for his Ph.D. thesis. He is currently a Postdoctoral Researcher with PES at ETH Zurich and his research interests include, inter alia, ultra-compact and -efficient three-phase ac-dc and dc-ac converter systems, extremely lightweight dc-dc converters for airborne applications, single-stage HF isolated ac-dc and ac-ac converters, and loss modelling of ferroelectric class II MLCCs.

Valentin Marugg received the B.Sc. and M.Sc. degrees in electrical engineering and information technology from the Swiss Federal Institute of Technology (ETH), Zurich, Switzerland, in 2020 and 2022, respectively, where he focused on power electronics and high voltage technology. He also spent a semester with Purdue University, Indiana, USA, as an exchange student. During his studies, he worked during one year with ABB Traction, Turgi, Switzerland, as an intern. Currently, he is a Junior R&D Engineer with ABB

Traction, focusing on gate-driver development.

Thomas Langbauer (S'18-M'22) received his B.Sc. in 2015 and M.Sc. degree in 2018 in electrical engineering from Graz University of Technology. Since 2018 he is working for Silicon Austria Labs within the Power Electronics Divison. He contributed to the Tiny Power Box project, which was aiming for highest power density for a bidirectional onboard charger for electric cars. From 2021 to 2022 he was an academic guest at the Power Electronic Systems Laboratory at ETH Zurich for six months. Currently, he is finalizing

his PhD thesis, which is supervised at the Electric Drives and Machines Institute at Graz University of Technology. His main research interests are charging technologies and power dense converters including modulation schemes and control design.

Johann W. Kolar (F'10) received his M.Sc. and Ph.D. degree (summa cum laude - promotio sub auspiciis praesidentis rei publicae) from the University of Technology Vienna, Austria, in 1997 and 1999, respectively. Since 1984, he has been working as an independent researcher and international consultant in close collaboration with the Vienna University of Technology, in the fields of power electronics, industrial electronics and high performance drive systems. He was appointed Assoc. Professor and Head of the Power Electronic

Systems Laboratory at the Swiss Federal Institute of Technology (ETH) Zurich on Feb. 1, 2001, and was promoted to the rank of Full Prof. in 2004. Dr. Kolar has proposed numerous novel converter concepts incl. the Vienna Rectifier, the Sparse Matrix Converter and the Swiss Rectifier, has spearheaded the development of x-million rpm motors, and has pioneered fully automated multi-objective power electronics design procedures. He

has supervised 80+ Ph.D. students to completion, has published 1000+ journal and conference papers and 4 book chapters, and has filed 200+ patents in the course of international industry research collaborations. He has presented 40+ educational seminars at leading international conferences and has served as IEEE PELS Distinguished Lecturer from 2012 - 2016. He has received 40+ IEEE Transactions and Conference Prize Paper Awards, the 2014 IEEE Power Electronics Society R. David Middlebrook Achievement Award, the 2016 IEEE PEMC Council Award, the 2016 IEEE William E. Newell Power Electronics Award, the 2021 EPE Outstanding Achievement Award and 2 ETH Zurich Golden Owl Awards for excellence in teaching. He is a Fellow of the IEEE and was elected to the U.S. National Academy of Engineering as an international member in 2021. The focus of his current research is on ultra-compact/efficient WBG converter systems, ANN-based design procedures, Solid-State Transformers, ultra-high speed drives, bearingless motors, and life cycle analysis of power electronics converter systems.